## A PASSIVE 2ND-ORDER SIGMA-DELTA MODULATOR FOR LOW-POWER ANALOG-TO-DIGITAL CONVERSION

by Angsuman Roy R. Jacob Baker

#### A BRIEF ROADMAP

- Need for Low Power  $\sum -\Delta$  ADCs

- **Review of Basic**  $\sum -\Delta$  **Modulator Topologies**

- **Proposed**  $\sum -\Delta$  Modulator Topology

- Circuit Design and Layout

- Test Results

# MARKET NEED FOR LOW POWER $\sum -\Delta$ ADCS

All these future devices and trends require low cost, low power ADCs. High resolution and precision are not prioritized. Passive  $\sum -\Delta$  ADCs can meet this need.

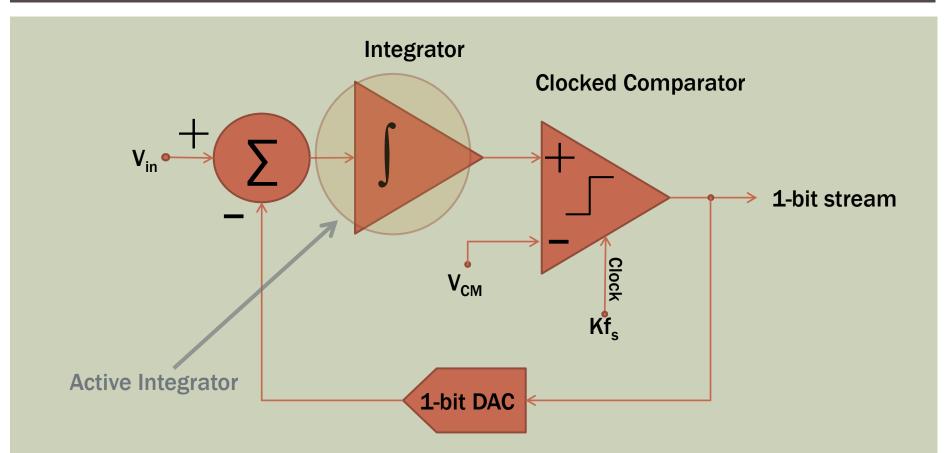

### REVIEW OF BASIC $1^{ST}$ ORDER $\sum -\Delta$ MODULATORS

Generally,  $\sum \Delta$  modulators use an active integrator to keep the voltage swing on the integrator's input to a minimum (ideally zero).

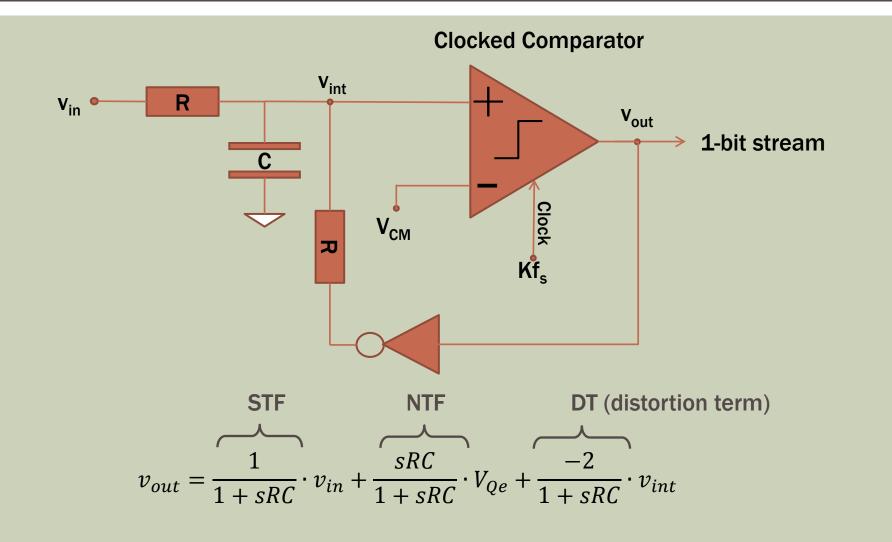

## **1<sup>ST</sup> ORDER PASSIVE** $\sum -\Delta$ **MODULATOR**

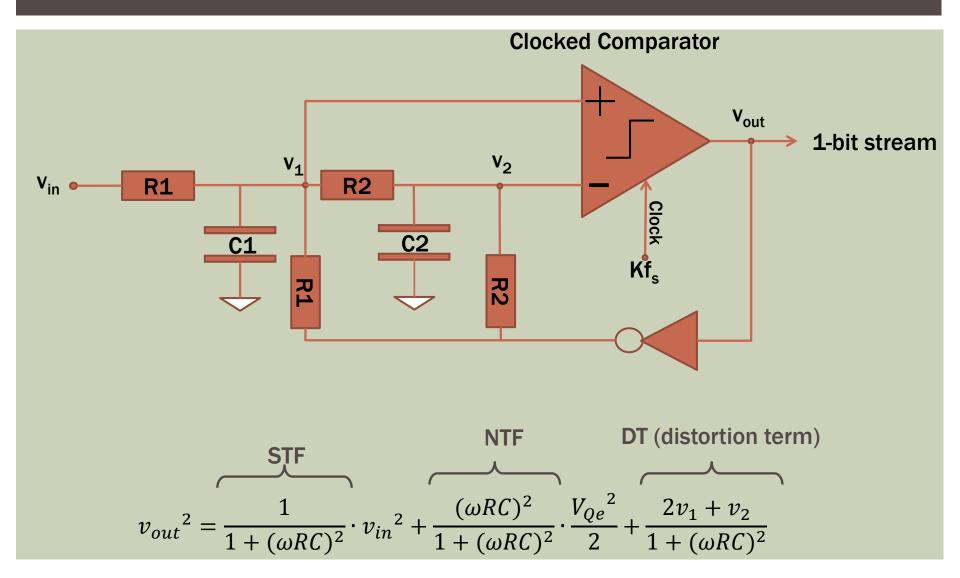

### CONVENTIONAL $2^{ND}$ ORDER PASSIVE $\sum -\Delta$ MODULATOR

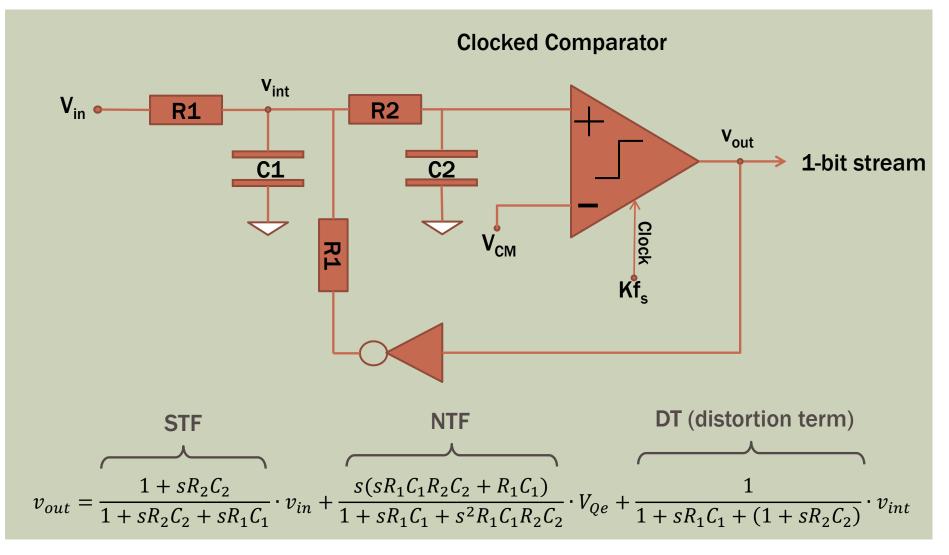

#### PROPOSED 2<sup>ND</sup> ORDER MODULATOR

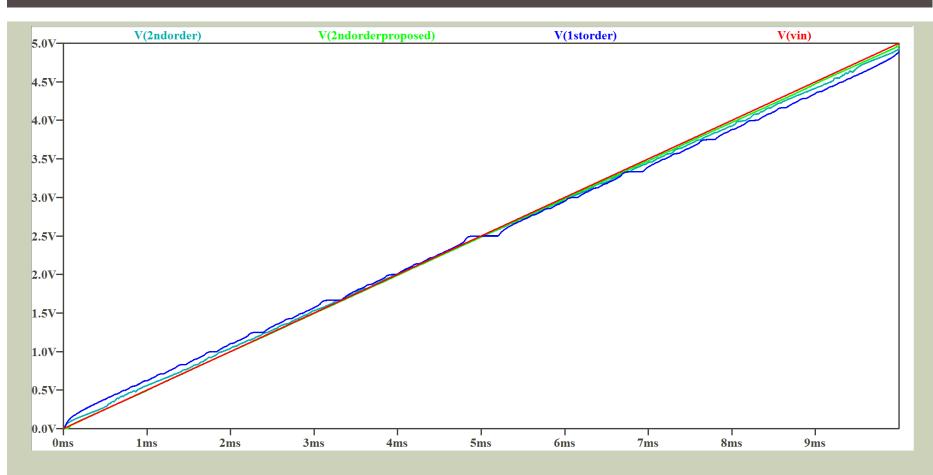

#### SPICE SIMULATION WITH IDEAL COMPONENTS

Linearity Comparison of  $\sum \Delta$  Modulator Topologies with a 10mS 0-5V Ramp Input

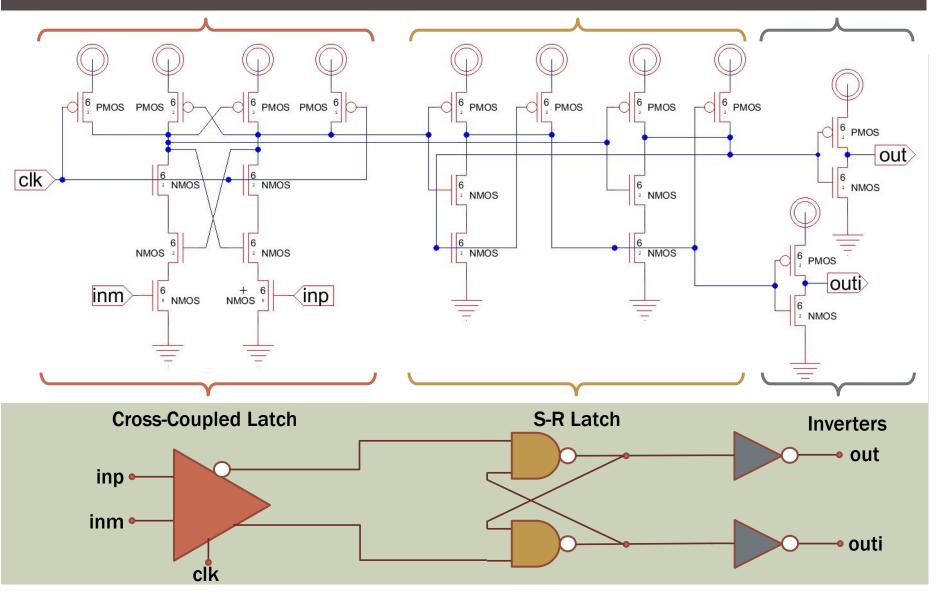

#### LOW POWER COMPARATOR DESIGN

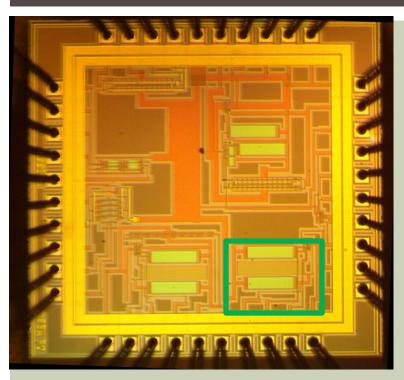

#### **CHIP LAYOUT**

#### **CHIP MICROGRAPHS**

Comparator

10pF

Capacitor

1 MΩ

Resistor

50 kΩ

Resistor

Micrograph of Entire Chip Area = 1.5 mm<sup>2</sup> Proposed Modulator in Green Micrograph of Proposed Modulator Area in View ≈ 400 µm<sup>2</sup>

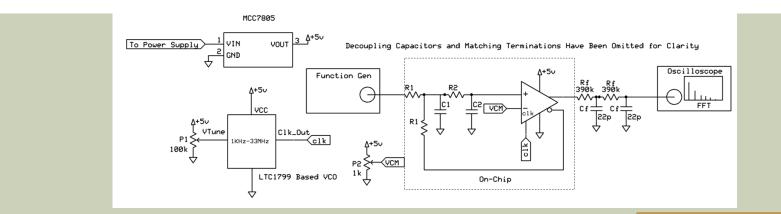

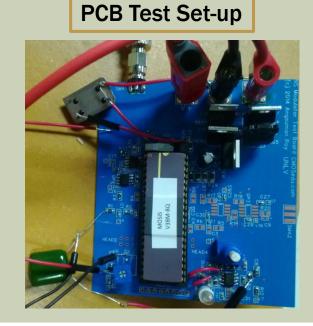

#### **TEST CIRCUIT**

"Dead-bug" Test Set-up

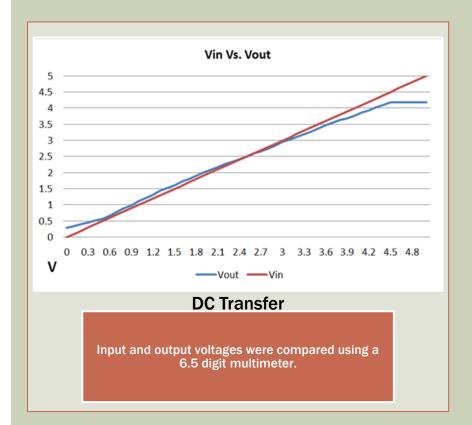

#### **MEASURED DC TEST RESULTS**

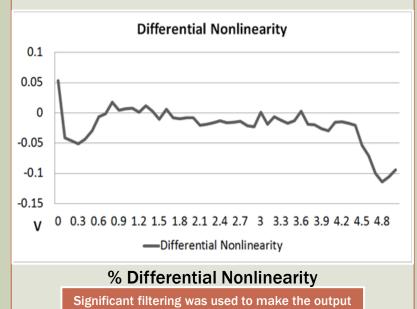

nearly static. DNL was calculated by dividing the measured incremental change by the ideal incremental change between data points.

#### **MEASURED AC TEST RESULTS**

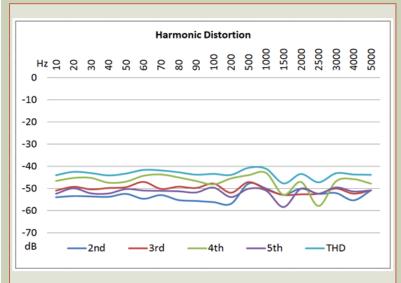

#### Harmonic Distortion (dB Below Fundamental)

Result measured using 8-bit oscilloscope FFT function. This limits SNR to around 50 dB.

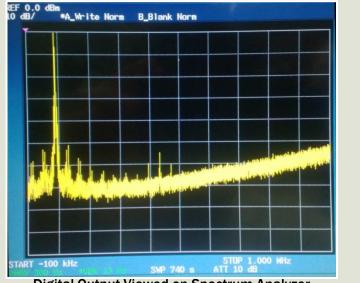

**Digital Output Viewed on Spectrum Analyzer**

Unfiltered digital output with 1kHz sine input. The spuriae free dynamic range is 50dB. The noise shaping is clearly visible.

#### **COMPARISONS TO OTHER WORKS**

| Parameter            | 2 <sup>nd</sup> Order<br>Passive ∑-∆<br>Modulator in<br>This Work<br>(Measured) | 2 <sup>nd</sup> Order Active<br>∑-∆ Modulator<br>in [5]<br>(Simulated) | 2 <sup>nd</sup> Order<br>Passive∑-∆<br>Modulator in<br>[2]<br>(Simulated) |

|----------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Process              | 500 nm                                                                          | 350 nm                                                                 | 350 nm                                                                    |

| Resolution<br>(ENOB) | 8-bit                                                                           | 12-bit                                                                 | 10-bit                                                                    |

| Power<br>Consumption | 100µW (typical)<br>@5V VCC                                                      | 120 μW<br>@2V VCC                                                      | 50 μW<br>@3.3V VCC                                                        |

| Signal<br>Bandwidth  | 5 kHz                                                                           | 1 kHz                                                                  | 4 kHz                                                                     |

| Clock Frequency      | 10 MHz                                                                          | 320 kHz                                                                | 1 MHz                                                                     |

[2] Guessab, S., P. Benabes, and R. Kielbasa. "Passive Delta-Sigma Modulator for Low-Power Applications," *MWSCAS '04*. (2004): 295-298.

[5] Gundel, Adnan, and Carr, William N. "A Micro Power Sigma-Delta A/D Converter in 0.35µm CMOS for Low Frequency Applications," *LISAT 2007*. (2007): 1-7.

#### CONCLUSIONS

#### Measurement Quality Limited by Test Equipment

Promising Topology for Low Power Applications Proposed Topology Should Scale Well Down to nm CMOS

Future Work Will Include More Detailed Comparisons Between Passive Topologies Future Work Will Attempt to Optimize Components to Increase ENOB