# A 3\*3 Multiplier Design using High Speed Energy Efficient Compressor Adder

Ravindra Chejara<sup>1</sup>, Rakesh Kumar<sup>2</sup>, Manish Verma<sup>3</sup>, Rohit Sharma<sup>4</sup>

<sup>14</sup>Research scholar, ECE, Sobhasria Group of Institution, Sikar

<sup>23</sup>Assistant Professor, ECE, Sobhasria Group of Institution, Sikar

Abstract- In digital signal processing systems multiplier is an important element. Wallace tree multipliers are considered as one of the high speed and efficient multipliers. In this paper, a multiplier is implemented using architecture for a Wallace tree multiplier. The implemented design comprises of 4:2 compressors. We have used the Tanner EDA Tool with version 14.1 in 180nm technology. The 4-2 compressor adder is simulated for supply voltage ranging from 1v-3v and various parameters are calculated, such as, power, delay and power delay product (PDP). The multiplier circuit is simulated at 180nm technology at 1.8v.

*Index Terms-* Multiplier, Multiplexer, Compressor Adder, Tanner tool.

#### I. INTRODUCTION

The prominence and request of high speed electronic systems are ceaselessly expanding step by step. Thus the improvement of a quick and productive system design has been a subject of enthusiasm of VLSI design engineers over decades. A processing component called compressor is broadly utilized as a part of high speed system. In this way the popularity and request of high speed compressors are quickly expanding in numerous parts of a digital system, particularly in digital signal processors, digital filters, microprocessors, motion estimation accelerators and so forth. VLSI designers have designed different kinds of 3-2, 4-2, 4-3, 5-2, 5-3, 6-3, 7-2, 7-3 and so forth compressors. The normal interconnection and simple structure make the 4-2 compressor appropriate for quick digital computational circuits.

Adder compressors have been utilized to implement math and digital signal processing (DSP) circuits for low power and high performance applications. Compressors are additionally utilized as a part of multiplier designs. Multipliers are structured into three capacities: partial-product generation, partial-product accumulation and final addition. The primary wellspring of power, delay and zone originated from the partial-product accumulation stage. Compressors ordinarily implement this stage since they add to the diminishment of the partial products (decreasing the quantity of adders at the final stage) and furthermore add to lessen the critical path which is imperative to keep up the circuit's performance.

In this paper a 4\*4 multiplier is designed using 4-2 compressor adder. In section 2,description and design of

compressor module using 8T XNOR/XOR is presented. The section 3 describes the multiplier designed by using 4-2 compressor and discusses the results ,simulation and finally the paper is concluded by the Section 4.

### II. COMPRESSOR ADDER

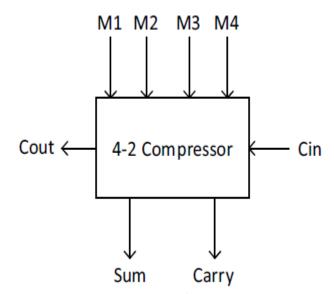

A 4-2 compressor is a combinatory device which compresses four partial products into two partial products. The block diagram of a 4-2 compressor is shown in Fig1. It accepts five inputs in particular M1, M2, M3, M4 and Cin; and generates three outputs, viz. Sum, Carry and Cout. Design of a 4-2 compressor with two 8T XOR-XNOR modules and four MUXs based on transmission gate logic is described. To implement the XOR-XNOR module a total of eight transistors are used.

Fig.1: Block diagram of 4-2 compressor

In XOR- XNOR module, the inverter consisting of MP1 and MN1 transistors generates the complement of input Y. The output of this inverter controls the second inverter consisting of transistors MP2 andMN2. XNOR of X and Y is generated by the second inverter with a problem of voltage degradation for X=0, Y=1 and X=Y=1. Level restoring pass transistors MP3 and MN3 are used to avoid this problem .In this module when inputs X=Y=0, the transistors MP1 and MP2 are turned on and output (XNOR) is at logic high. When inputs X=0 and

# IJRECE VOL. 6 ISSUE 3 ( JULY - SEPTEMBER 2018)

Y=1, transistors MP2, MP3, MN1 and MN3 are turned on and a logic low is passed to the output node. Again for inputs X=1 and Y=0, transistors MP1 and MN2 are turned on and output node shows a logic low. Finally when inputs X=Y=1,

# ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE)

transistors MP3, MN1, MN2 and MN3 are turned on and output is at logic high level.

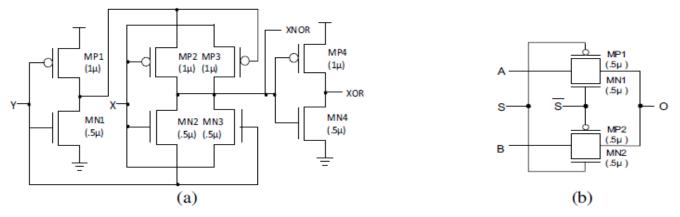

A MUX implemented with transmission gate logic is shown in Fig2.

Fig.2: 8T XOR-XNOR module (b) Transmission gate MUX.

The Fig3 shows the schematic design of 4-2 compressor using XNOR/XOR gates and Mux's using Transmission Gate. The sum, carry, and Carry out is generated as shown in the fig

below. The compressor circuit consists of 36 transistors for sum, carry and cout operation.

Fig.3: Schematic of 4-2 compressor adder

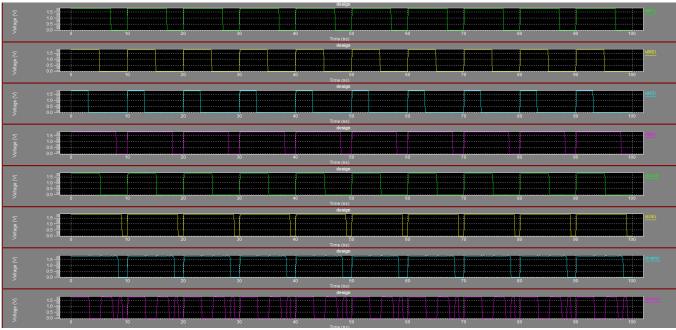

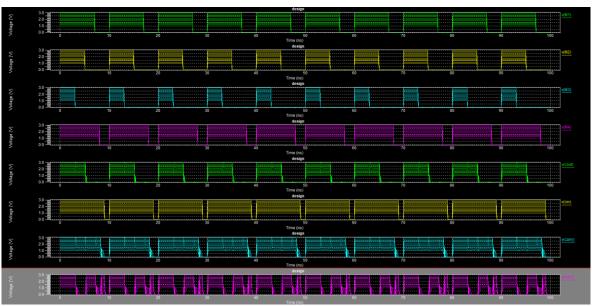

The waveform of the described architecture simulated at 1.8v is shown in the Fig4  $\,$

Fig.4: Waveform of 4-2 compressor adder

The table shows the 4-2 compressor parameters with supply variation ranging from 1v-3v at 180nm technology. The delay

,power, PDP, Energy, EDP are calculated and illustrated below

Table :1 Performance Comparison of compressor at various supply voltages

| Parameters     |         | 1.0v    |    | 1.2v     |   | 1.4v    |     | 1.6v    | 1.8v    |    |

|----------------|---------|---------|----|----------|---|---------|-----|---------|---------|----|

| Power (u)      |         | 12.093  |    | 18.364   |   | 25.916  |     | 34.641  | 44.490  | )  |

| Delay_cout(n)  |         | 0.38880 |    | 0.27687  |   | 0.21625 | (   | 0.17984 | 0.1578  | 38 |

| Delay_carry(n) |         | 0.86374 |    | 0.65038  |   | 0.50044 | (   | 0.40753 | 0.3516  | 53 |

| Delay_sum(n)   |         | 0.71364 |    | 0.46241  |   | 0.33738 | (   | 0.26636 | 0.2216  | 52 |

| Energy (p)     |         | 1.2093  |    | 1.8364   |   | 2.5916  |     | 3.4641  | 4.4490  | )  |

| EDP_cout (z)   |         | 0.47018 |    | 0.50846  |   | 0.56043 | (   | 0.62298 | 0.7024  | 13 |

| EDP_carry (z)  |         | 1.0445  |    | 1.1944   |   | 1.2969  |     | 1.4117  | 1.5644  | ļ  |

| EDP_sum (z)    |         | 0.86302 |    | 0.84919  |   | 0.87435 |     | 0.92269 | 0.9859  | 9  |

| PDP_cout (f)   |         | 4.7018  |    | 5.0846   |   | 5.6043  |     | 5.2298  | 7.0243  | 3  |

| PDP_carry (f)  |         | 10.445  |    | 11.944   |   | 12.969  |     | 14.117  | 15.644  | ļ  |

| PDP_sum (f)    |         | 8.6302  |    | 8.4919   |   | 8.7435  | 9   | 9.2269  | 9.8599  | )  |

| Parameters     | 2.0v    | 2.2v    | 2. | .4v      | 2 | .6v     | 2.8 | Bv      | 3.0v    |    |

| Power (u)      | 56.759  | 70.220  | 8  | 6.275    | 1 | 04.42   | 12  | 4.18    | 148.61  |    |

| Delay_cout(n)  | 0.14250 | 0.13330 | 0. | .12690   | 0 | .12198  | 0.1 | 1805    | 0.13757 |    |

| Delay_carry(n) | 0.31124 | 0.28186 | 0. | .26008   | 0 | .24340  | 0.2 | 22988   | 0.21977 |    |

| Delay_sum(n)   | 0.19413 | 0.17322 | 0. | .16202   | 0 | .15411  | 0.1 | 14826   | 0.14482 |    |

| Energy (p)     | 5.6759  | 7.0220  | 8. | 8.6275   |   | 10.442  |     | .418    | 14.861  |    |

| EDP_cout (z)   | 0.80881 | 0.93604 | 1. | 1.0948   |   | 1.2737  |     | 1660    | 2.0445  |    |

| EDP_carry (z)  | 1.7665  | 1.9792  | 2. | 2.2438 2 |   | .5415   | 2.8 | 3546    | 3.2661  |    |

| EDP_sum (z)    | 1.1019  | 1.2164  | 1. | .3978    | 1 | .6091   | 1.8 | 3410    | 2.1522  |    |

# IJRECE VOL. 6 ISSUE 3 ( JULY - SEPTEMBER 2018) ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE)

| PDP_cout (f)  | 80.881 | 9.3604 | 10.948 | 12.77  | 14.660 | 20.445 |

|---------------|--------|--------|--------|--------|--------|--------|

| PDP_carry (f) | 7.665  | 19.792 | 22.438 | 25.415 | 28.546 | 32.661 |

| PDP_sum (f)   | 11.019 | 12.164 | 13.978 | 16.091 | 18.410 | 21.522 |

Fig.5: Simulated waveform of 4-2 compressor at various supply voltage

The Fig.5 shows the waveform of 4-2 compressor with supply variation from 1v-3v at 180nm technology

#### III. MULTIPLIER

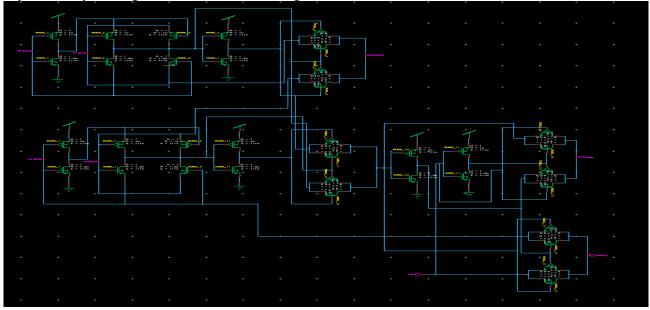

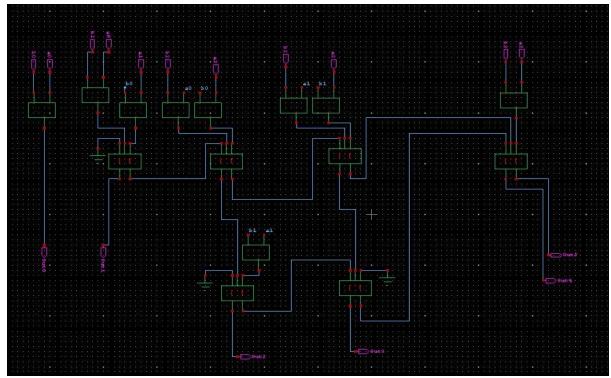

A 3\*3 multiplier is designed by using 4-2 compressor adder circuit as shown in Fig 6. The multiplier multiplies two 3-bit inputs and generates 6-bit output. The two 3 bit inputs are multiplied using AND gate. In Wallace tree multiplier bits are multiplied according to their weights. The weight of a wire is the radix (to base 2) of the digit that the wire carries. The multiplier module consists of AND gate,4-2 compressor adder used as full adder. The compressor adder is used as the full adder by grounding the two bits of five bits. The first AND gate takes weight 0 i.e. a0 and b0, and the first bit of the multiplication is taken from it. The second and third AND

gate takes bits of weight 1 i.e. a0\*b1 and a1\*b0 and this is given to the compressor as input. The compressor gives two outputs-sum and carry. The sum output of this compressor module is the second output bit of multiplication and the carry of the compressor adder is forwarded to the next compressor module in the next stage i.e. weight 2. The 6-bit output is calculated in the same way.6<sup>th</sup> bit of the multiplication is taken from the final carry. The results are checked for 200ns with on and off time as 50ns at 1.8v and checked for 4 different combinations:

- 7\*7

- 6\*5

- 2\*4

- 3\*0

Fig.6: schematic for 3\*3 multiplier using 4-2 compressor.

The Fig7 is the waveform of the multiplier for the four combinations stated above simulated at 1.8v for 200ns.

Fig.7: Waveform for 4\*4 multiplier

# IV. CONCLUSION

The Wallace tree multipliers can be solved & analyzed using a new modified method of Wallace tree construction using

compressors. This modified design of multiplier which consist of 4:2 compressor reduces the complexity and reduce the time

## IJRECE VOL. 6 ISSUE 3 ( JULY - SEPTEMBER 2018)

delay. Multiplier using Compressor have small increase in area and power but the time delay is less compare to conventional Wallace Tree Multiplier. As the Compressor order is increased the time delay reduces respectively. Hence for small delay requirement Wallace Tree Multiplier using compressor is suggested. The simulation is done using Tanner EDA tool with 180nm technology.

#### V. REFERENCES

- [1]. S. Kumar and M. Kumar, "4-2 Compressor design with New XOR-XNOR Module," 4thInternational Conference on Advanced Computing & Communication Technologies (ACCT), pp. 106-111, 2014.

- [2]. P. Bhattacharyya, B. Kundu, S. Ghosh, V. Kumar and A. Dandapat, "Performance Analysis of a Low-Power High-Speed Hybrid 1-bit Full Adder Circuit," IEEE Transactions on Very Large

- Scale Integration (VLSI) Systems, vol. 23, pp. 2001-2008, 2015. [3]. Y.Kim, Y.Zhang, and P. Li, "An energy efficient approximate adder with carry skip for error resilient neuromorphic VLSI systems," in proc. of International conference on Computer-Aided Design (ICCAD), Nov. 2013, pp. 130-137.

- [4]. A. Pishvaie, G. Jaberipur, and A. Jahanian, "High Performance CMOS (4:2) compressors," International journal of electronics, vol. 101, no. 11, pp. 1511-1525 Jan. 2014.

- [5]. KunipriyaMorghade, Pravin Dakhole, "Design of fast vedic multiplier with fault diagnostic capabilities", Communication and Signal Processing (ICCSP) 2016 International Conference on, pp. 0416-0419, 2016.

- [6]. Radheshyam Gupta, Rajdeep Dhar , K. L. Baishnab ,Jishan Mehedi "Design of high performance 8 bit Vedic Multiplier using compressor". International Conference on Advances in Engineering and Technology (ICAET 2014)

# ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE)

- [7]. R. Marimuthu, Y. Elsie Rezinold, P. S. Mallick "Design and Analysis of Multiplier Using Approximate 15-4 Compressor", 13 December 2016. DOI 10.1109/ACCESS.2016.2636128, IEEE Access.

- [8]. C.-H. Lin, and I.-C. Lin, "High accuracy approximate multiplier with error correction," in proc. of IEEE 31st International Conference on Computer Design (ICCD), Oct. 2013, pp. 33 -

- [9]. Y. Bansal, and C. Madhu, "A novel high-speed approach for 16x16 vedic multiplication with compressor adders," Computers and Electrical Engineering, vol. 49, pp. 39-49, Jan. 2016.

- [10]. A. Momeni, J. Han, P. Montuschi, and F. Lombardi, "Design and analysis of approximate compressors for multiplication.

- [11].Ron S. Waters, Earl E. Swartzlander"A Reduced Complexity Wallace Multiplier Reduction", IEEE Transactions on Computers (Volume: 59, Issue: 8, Aug. 2010).

- [12]. Tiago Schiavon, Guilherme Paim, Mateus Fonseca, Eduardo Costa , Sergio Almeida "Exploiting adder compressors for power-efficient 2-D approximate DCT realization", IEEE 7th Latin American Symposium on Circuits & Systems (LASCAS),

- [13]. Raphael Dornelles, Guilherme Paim, Bianca Silveira, Mateus Fonseca, Eduardo Costa, Sergio Bampi "A power-efficient 4-2 Adder Compressor topology", 15th IEEE International New Circuits and Systems Conference (NEWCAS), 2017

- [14].J.H. Satyanarayana , K.K. Parhi "A theoretical approach to estimation of bounds on power consumption in digital multipliers", IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing (Volume: 44, Issue: 6, Jun 1997)

- [15].P. Saha, P. Samanta, D. Kumar "4:2 and 5:2 Decimal Compressors", 7th International Conference on Intelligent Systems, Modelling and Simulation (ISMS), 2016.