# GLOBAL ENHANCED AND CONSISTANT ADDRESS METHODS BASED ON MEMORY, FFT PROCESSOR DESIGN

\* S SHRUTHI, \*\*Dr MD SALAUDDIN

\*MTech student, Dept of ECE, JBIET, Hyderabad, TS, India.

\*\* Associate Professor & HOD, Dept of ECE, JBIET, Hyderabad, TS, India.

ABSTRACT - A rapid Fourier change is any type of quick formula for calculating the DFT. The advancement of FFT formulas had a remarkable influence on computational facets of signal handling as well as used scientific research. The decimation-in time (DIT) rapid Fourier change really usually has benefit over the decimation-in-frequency (DIF) many real-valued applications, FFT for like speech/image/video handling, biomedical signal handling, and also time collection evaluation, and so on, considering that it does not call for any type of outcome reordering. It changes the index to a multidimensional vector for reliable calculation. By managing the index vector to please the "vector opposite" practices, the GMR formula could sustain not just in-place plan for both calculation as well as I/O information for constant information circulation to reduce the memory dimension vet likewise multibank memory frameworks to raise the optimum throughput without memory dispute. We made 2 FFT instances in long-lasting development system to validate the schedule of the address system, consisting of a 2n (128-- 2048)-factor FFT device as well as a 35 various factor (12-- 1296) DFT device. Compared to previous collaborate with comparable address systems, this paper sustains extra generalised sizes and also accomplishes a lot more adaptable throughput.

Keywords: FFT, DIT, DIF, Image processing, Vector reverse, GMR algorithm, Address scheme.

## I. INTRODUCTION

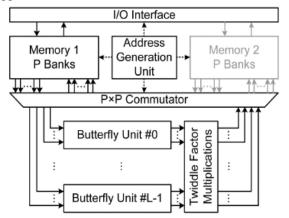

There has been an increasing interest in the computation of fast Fourier transform (FFT) of real-valued signals, referred to as real fast Fourier transform (RFFT), and in-place fast Fourier transform (IFFT) of Hermitic an symmetric signals, referred to as real in-place fast Fourier transform (RIFFT). This is because most of the physical signals, such as biomedical signals, are real. The real-valued signals exhibit conjugate symmetry, giving rise to redundancies. Memorybased FFT processors are composed of a kernel processing unit and several memory blocks, the hardware requirement and power consumption of which are both lower than pipelined FFT processors and we adopt the memory-based FFT in our work. The typical FFT processor is composed of butterfly units, address generator unit, control unit and memories. Butterfly units are composed of complex multipliers and adders. And one complex multiplier needs four real multipliers and two adders, thus the butterfly units

are the speed bottleneck in FFT processor. The memorybased processor design, minimizing the necessary memory size is effective for area reduction since the memory costs a significant part of the processor. On the other hand, the FFT processor usually adopts on-chip static random access memory (SRAM) instead of external memory. The reason is the high-voltage I/O and the large capacitance in the printercircuit-board (PCB) trace would increase power consumption for external memory. Besides the power issue, using external memory also increases the PCB-level verification cost for end-product manufacturers. Therefore, it is a trend to use the on-chip SRAM for FFT processors and to conduct FFT optimization for better system-level integration. The mixed-radix FFT is proposed to optimize the memory-based FFT processor design. It supports not only in-place policy to minimize the necessary memory size for both butterflies output and I/O data but also multibank memory structure to increase its maximum throughput to satisfy more system applications without memory conflict. After the algorithm is introduced, we take the 16 -point FFT as an illustrative example. Finally, a low complexity hardware implementation of an index vector generator is also proposed for our algorithm.

## II. RELATED STUDY

A DFT decomposes a sequence of values into components of different frequencies. This operation is useful in many fields (see discrete Fourier transform for properties and applications of the transform) but computing it directly from the definition is often too slow to be practical. An FFT is a way to compute the same result more quickly: computing a DFT of N points in the naive way, using the definition, takes O(N 2) arithmetical operations, while an FFT can compute the same result in only O(N log N) operations. The difference in speed can be substantial, especially for long data sets where N may be in the thousands or millions in practice, the computation time can be reduced by several orders of magnitude in such cases, and the improvement is roughly proportional to  $N/\log(N)$ . This huge improvement made many DFT-based algorithms practical; FFTs are of great importance to a wide variety of applications, from digital signal processing and solving partial differential equations to algorithms for quick multiplication of large integers. Pipelined architectures contain either feed forward or feedback data paths. The feedback architectures have been referred to as single path delay feedback, and the feed

forward architectures have been referred to as multipath delay commentator. Much research has been carried out on the design of pipelined architectures for computing the FFT of complex and real-valued signals for high-throughput applications.

Fig.2.1. Architecture of a multiple-PE, memory-based FFT processor.

## III. AN OVERVIEW OF PROPOSED SYSTEM

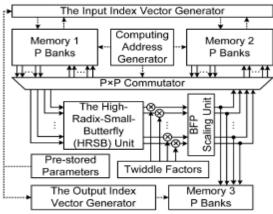

It was as soon as thought that real-input DFTs can be extra effectively calculated using the distinct Hartley change, however it was consequently suggested that a specialized real-input DFT formula (FFT) could usually be located that needs less procedures compared to the equivalent DHT formula for the exact same variety of inputs. Braun's formula (over) is one more technique that was at first recommended to capitalize on actual inputs; however it has actually not verified preferred. FFT CPU could make use of radix-2 formula, radix-4 formula, split-radix formula and more. In this paper, we take on the radix-4 formula. Fig. 1 reveals the leading 1024-point style of FFT CPU, which is made up of control device, address create system, twiddle variable angle generator, flexible recoding CORDIC (ARC) based-butterfly system, directing network, multiplexers (Mux) and also memory financial institutions. The control system regulates various other FFT CPU systems. Via mux1, the input information are chosen right into  $mux2 \sim 5$ . Mux2  $\sim$  5 are made use of to pick the signals passing to memory financial institutions from the input information and also the computed information after directing network. Address create system produces the compose addresses and also check out addresses of memory financial institutions. As the FFT cpu is ROM-free twiddle element, the twiddle variable angle generator manages creating the twiddle consider real-time. Directing network is utilized to provide operands. The outcomes are the efficient outcomes of the mux6  $\sim$  9. Every example is stood for by utilizing the 9-bits of details. The 8-bits are for the info and also 1-bit is utilized for the indicator little bit depiction. The variety of examples is 16, given that both phases of complicated radix-4 butterfly reproductions are called for. For the every single phase calls for the various twiddle factors. The needed

#### ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE)

twiddle variables are provided by utilizing LUT table. After the 4th phase estimation we could obtain the 16-samples outcomes with actual as well as fictional components.

Fig.3.1. Block diagram of FFT Prosessor.

The suggested approach calls for less calculation cycles compared to the others. Thus, our FFT possesses the highest possible handling rate. Though our approach takes in even more memory, it could combine the best outcomes, which minimizes the trouble to review the accuracy of the FFTs. There are 13 complicated adders, 5 consistent multipliers for coefficient reproductions, and also 5 complicated multipliers for twiddle element reproductions in the merged butterfly core. Hence, the sources in the PE are dual. The PE in inhabits practically the exact same equipment as ours. Nevertheless, it utilizes much more control multiplexers as well as barriers, as well as the regulating system is much more difficult.

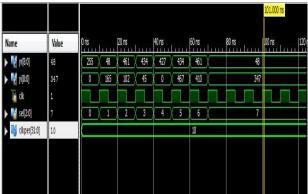

Fig.3.2. simulation waveform for top module.

#### IV. CONCLUSION

We offer memory-based FFT applications with generalized effective conflict-free address plans. Address plans for various FFT sizes are incorporated in this paper to sustain FFT handling for different systems. The memory financial institution as well as address could be created by modulo as well as reproduction procedures of the disintegration figures. For both SPP as well as NSPP FFTs, high-radix formula and also parallel-processing method could be made use of to boost the throughput. And also the address system for FFTs used with PFA is checked out. In addition, a decay

approach, called HRSB, is created to match the high-radix formula. Complete equipment styles for the FFTs in LTE systems are detailed, consisting of the index vector generator, the butterfly engine, as well as the linked WTFA core. The application results as well as contrasts are additionally provided.

#### V. REFERENCES

- [1]. J. Lee, H. Lee, S. I. Cho, and also S. S. Choi, "A high-speed 2 identical radix-24 FFT/IFFT cpu for MB-OFDM UWB systems," in Proc. IEEE Int. Symp. Circuits Syst., May 2006, pp. 4719-- 4722.

- [2]. M. Ayinala, M. Brown, as well as K. K. Parhi, "Pipelined parallel FFT designs by means of folding makeover," IEEE Trans. Huge Scale Integr. (VLSI) Syst., vol. 20, no. 6, pp. 1068-- 1081, Jun. 2012.

- [3]. R. Radhouane, P. Liu, as well as C. Modin, "Minimizing the memory demand for continual circulation FFT execution: Continuous circulation combined setting FFT (CFMM-FFT)," in Proc. IEEE Int. Symp. Circuits Syst., May 2000, pp. 116--119

- [4]. B. G. Jo as well as M. H. Sunwoo, "New continuous-flow mixed-radix (CFMR) FFT cpu utilizing unique inplace method," IEEE Trans. Circuits Syst. I, Reg. Documents, vol. 52, no. 5, pp. 911-- 919, May 2005.

- [5]. A. T. Jacobson, D. N. Truong, and also B. M. Baas, "The layout of a reconfigurable continuous-flow mixed radix FFT cpu," inProc. IEEE Int. Symp. Circuits Syst., May 2009, pp. 1133-- 1136.

- [6]. C. F. Hsiao, Y. Chen, and also C. Y. Lee, "A generalised mixed-radix formula for memory-based FFT cpus," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 57, no. 1, pp. 26--30, Jan. 2010.

- [7]. P.-Y. Tsai and also C.-Y. Lin, "A generalised conflict-free memory attending to system for continuous-flow parallelprocessing FFT cpus with rescheduling," IEEE Trans. Huge Scale Integr. (VLSI) Syst., vol. 19, no. 12, pp. 2290-- 2302, Dec. 2011.

- [8]. A. M. Despain, "Very quick Fourier change formulas equipment for execution," IEEE Trans. Comput., vol. C-28, no. 5, pp. 333-- 341, \ May 1979.

- [9]. C. L. Wey, S.-Y. Lin, and also W. C. Tang, "Efficient memory-based FFT cpus for OFDM applications," in Proc. IEEE Electro/Inf. Technol., May 17-- 20, 2007, pp. 345-- 350.

- [10]. Jaguar II Variable-Point (8-1024) FFT/IFFT, Drey Enterprise Inc., Crosslake, MN, 1998.

- [11].R. Radhouane, P. Liu, as well as C. Modlin, "Minimizing the memory demand for continual circulation FFT execution: Continuous circulation combined setting FFT (CFMM-FFT)," in Proc. IEEE Int. Symp. Circuits Syst., May 2000, vol. 1, pp. 116-- 119.