# Delay and power analysis of bundled SWCNT interconnects with variation in driver size

Yograj Singh Duksh

Department of Electronics and Instrumentation Engineering, Faculty of Engineering and Technology, Mahatma Jyotiba Phule Rohilkhand University, Bareilly, India (E-mail: ysdaksh.ei@mjpru.ac.in)

Abstract— In this paper, the propagation delay and power consumption for bundled SWCNT and Cu interconnects are analyzed by varying the driver size at 32nm and 22nm technology node. The variation in driver size approach is used to minimize the propagation delay and power consumption. equivalent circuit model for bundled SWCNT An interconnects is proposed to estimate the propagation delay and power consumption at global length of interconnects. A simple approximation of an RLC interconnect line for bundled SWCNT interconnect is obtained by using pi  $(\pi)$  model to achieve better accuracy for estimating propagation delay and power consumption. The propagation delay and power consumption for bundled SWCNT interconnects are analyzed, estimated and compared with Cu interconnects by running the SPICE simulations. SPICE simulation results demonstrate that the propagation delay ratio  $(T_{swentb}/T_{Cu})$  is lesser for smallest value of driver size and the ratio of average power consumption  $(P_{swentb}/P_{Cu})$  is lowest in between 800µm to 1000µm length of interconnect at both technology nodes.

*Keywords*—Delay; Power Consumption; SWCNT Interconnect; π-Model; Driver.

# I. INTRODUCTION

The resistivity of copper is increasing rapidly due to the combined effect of enhanced electron-surface, grain boundary scattering, and the presence of highly resistive diffusion barrier layer in current deep-submicron technology node [1]. The steep rise in parasitic resistance of copper interconnects poses serious challenges for interconnect reliability and delay at the global level [2]. It has a significant impact on the performance and reliability of VLSI circuits and systems. In order to overcome these problems, researchers are forced to find an alternate material used for on-chip interconnects at global level. Recently, carbon nanotubes (CNTs) have been reported as a promising material for interconnects due to its long mean free path of about several micrometers, high current densities greater than 10<sup>9</sup> A/cm<sup>2</sup>, and high thermal stability than copper [3]. These unique properties create a lot of interest among researchers to use the CNTs for future VLSI interconnects.

CNTs consist of the hexagonal graphene sheets rolled up of hollow cylinders. CNTs can be categorized into single-walled carbon nanotubes (SWCNTs) and multi-walled carbon nanotubes (MWCNTs). Depending on the chirality, CNTs can be either metallic or semiconducting. The diameter of SWCNTs ranging from 1 to 5nm and length from 2 to 10nm, while the diameter of MWCNTs ranging from few to hundreds of nanometers and length of several microns. The SWCNTs consist of single shell, whereas MWCNTs consist of various concentric shells. CNTs are one-dimensional (1D) system of electrons that provide extraordinary electrical and thermal properties. Since the electrons can move in 1D and scattered only backward, therefore the scattering of nanotubes in the phase space is very limited [4]. The mean free path (mfp) of the metallic nanotubes is about of  $10^3$  to  $10^4$  nm at room temperature, whereas in three dimensional (3D) metallic copper wire, the electrons can be backward by a series of small angle scattering and the mfp is ranging of 40 nm [5-6]. Due to these extraordinary electrical, and thermal properties, CNT based interconnects play an important role to minimize the delay and improve the performance of circuits and systems in the modern era of nanoelectronics.

Kreupl et al. [3] demonstrated the possible implementations of CNTs in interconnect applications. In recent past, several researchers reported that an isolated SWCNT could not achieve better performance than copper interconnect due to of its higher resistance. Therefore, researchers have always focused on CNT bundles to improve the interconnect performance [3, 7]. Raychowdhury and Roy [8-9] presented a realistic RLC model for metallic SWCNTs and analyzed the impact of SWCNTs on the performance of ultra-scaled digital VLSI design. Based on the realistic *RLC* models, Naeemi, Sarvari, and Meindl [10-11] compared the performance of bundled SWCNT and copper interconnects for the first time. It is observed that the SWCNT bundles can have adequately large propagation speed and outperform than the copper in terms of resistance and delay. The authors also demonstrated that the performance enhancement increases as the length of interconnect increases or the feature size decreases. Later on, Srivastava and Banerjee [13] compared the performance of bundled SWCNT and copper interconnects by assuming large contact resistances. It is also observed that the SWCNTs can outperform copper in terms of resistance and can have adequately small kinetic inductance. It is also demonstrated that the performance of bundled SWCNT can outperform copper wire interconnects at global level. Later, based on physical models, Naeemi and Meindl [4] presented the distributed circuit models of SWCNTs and bundled SWCNTs that are valid for all voltages and currents. These models can be used for circuit simulations and compact modeling. Recently, Srivastava, Li, Kreupl and

Banerjee [12] reported a comprehensive and realistic evaluation of SWCNT bundle interconnects.

The variation in driver size is an important approach to minimize the propagation delay and power consumption. The propagation delay and power consumption for bundled SWCNT interconnects against conventional Cu interconnects are minimized at 32nm and 22nm technology nodes for various driver sizes. The parasitic components based on interconnect geometry and its equivalent circuit model of bundled SWCNT interconnect are described and discussed in Section II. The set up for simulation is presented in Section III. The propagation delay and power consumption for bundled SWCNT are analyzed and compared with traditional Cu interconnects by running the SPICE simulations in Section IV. Finally, conclusions are drawn in Section V.

## II. EQUIVALENT CIRCUIT MODEL OF BUNDLED SWCNT INTERCONNECTS

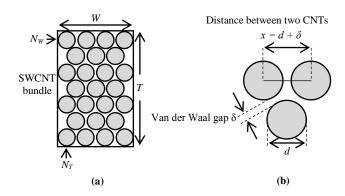

The bundled SWCNT interconnect is assumed to be composed of hexagonally densely packed identical metallic SWCNTs. Each SWCNT is surrounded by six immediate neighbours and their centres uniformly separated by inter-CNT distance 'x'. The schematic of bundled SWCNT, dense triangular packing of SWCNTs with Van der Waal gap ' $\delta$ ' are demonstrated in Fig. 1.(a) and (b).

Fig. 1.(a) Schematic of bundled SWCNT interconnect [12] (b) Dense triangular packing of SWCNTs with Van der Waal gap  $\delta$  [12]

The geometrical structure of densely packed bundled SWCNT interconnect, and Cu interconnect are identical as illustrated in Fig. 1(c). In the geometrical structure, the distance between two CNTs,  $x = d + \delta$ , is considered, where d (=1 nm) is the diameter of SWCNT and  $\delta$  (= 0.34 nm) is the Van der Waal gap between each CNT in the bundle. The two immediate adjacent wires (left and right) held at ground potential, parallel to SWCNT bundle are considered. The physical parameters such as wire width (W), spacing between adjacent CNTs (S), thickness of the bundle (T), and height from the ground plane to the SWCNT bundle (H), aspect ratio (=T/W), and dielectric constants are technology dependent. The spacing between the adjacent bundles is assumed to be equal to the bundle width and the thickness of the bundle is assumed to be equal to the

height from the ground plane to the bundle.  $N_W$  and  $N_T$  are the number of SWCNTs along the width and thickness in the SWCNT bundle, respectively, as shown in Fig. 1(a).

Fig. 1. (c) Equivalent geometrical structure of bundled SWCNT/Cu interconnect [12]

The total number ( $N_{CNT}$ ) of SWCNTs in a bundle can be expressed as [13]:

$$N_{CNT} = N_W N_T - N_T / 2$$

, for  $N_T$  is even (1)

$$N_{CNT} = N_W N_T - (N_T - 1)/2$$

, for  $N_T$  is odd (2)

where,

$$N_W = \operatorname{int}[(W - d)/x]$$

; and

$$N_T = \operatorname{int}\left[\frac{T-d}{\left(\sqrt{3}/2\right)x}\right] + 1$$

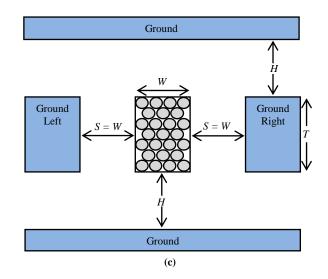

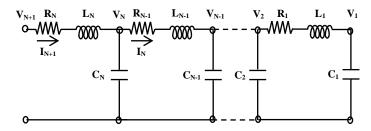

The equivalent circuit model of bundled SWCNT interconnect is employed for delay and power analysis as illustrated in Fig. 2 [12]. The modeling of bundled SWCNT interconnects and its parasitic resistance, inductance, and capacitance are explained below.

Fig. 2. Equivalent circuit model of bundled SWCNT interconnect for bundle length (l) greater than electron mean free path ( $\lambda$ ) [12]

# INTERNATIONAL JOURNAL OF RESEARCH IN ELECTRONICS AND COMPUTER ENGINEERING A UNIT OF I2OR 861 | P a g e

# A. Resistance of Bundled SWCNT Interconnect

The resistance  $(R_b)$  of SWCNT bundle interconnects can be evaluated as [12]:

$$R_b = \frac{R_{CNT}}{N_{CNT}} \tag{3}$$

where  $R_{CNT}$  is the total resistance of an isolated SWCNT. It is the sum of three different types of resistances: (1) metalnanotube contact resistant  $R_c$ ; (2) fundamental quantum resistance  $R_q$  (= $h/4e^2$ ); and (3) ohmic resistance due to scattering ( $R_o$ ) that occurs when the nanotube length (l) greater than the electron mfp ( $\lambda$ ). The ohmic resistance is distributed resistance along SWCNT interconnect and represented in per unit length. The contact resistance is in series with the quantum resistance and equally divided between the two-end contacts considered as lumped resistance. The total resistance of isolated SWCNT can be expressed as [12]:

$$R_{CNT} = R_c + R_q \text{ for } l < \lambda \tag{4}$$

$$R_{CNT} = R_c + R_a + l.R_o \text{ for } l >> \lambda$$

(5)

For the perfect metal-nanotube contact, the resistance ( $R_c$ ) is assumed to be very small and can be ignored for the delay and power analysis. The resistance of an isolated SWCNT is too high for implementing an interconnection [12]. Consequently, it is necessary to have a bundle of SWCNTs to lower the effective resistance and may work effectively as Nano scale VLSI interconnects.

#### B. Inductance of bundled SWCNT interconnect

The inductance  $(L_b)$  of bundled SWCNT interconnects of length *l* can be estimated as [12]:

$$L_b = \frac{L_{CNT} l}{N_{CNT}} \tag{6}$$

where  $L_{CNT}$  is the per unit length (p.u.l) total inductance of an isolated SWCNT. It is the sum of p.u.l kinetic inductance  $(L_k)$  and p.u.l magnetic inductance  $(L_m)$  of an isolated SWCNT. The p.u.l total inductance  $(L_{CNT})$  of CNT is the sum of p.u.l kinetic inductance  $(L_k)$  due to four non-interacting parallel conducting channels and p.u.l magnetic inductance  $(L_m)$  of an isolated SWCNT, can be expressed as [12]:

$$L_{CNT} = L_k + L_m \tag{7}$$

$$L_k = \frac{1}{4} \left( \frac{h}{2e^2 V_F} \right) \tag{8}$$

$$L_m = \frac{\mu}{2\pi} \cosh^{-1}\left(\frac{H}{d}\right) \tag{9}$$

where h, e, and  $V_F$  are the plank's constant, electronic charge, and Fermi velocity, respectively. H, and d, are height from ground plane to the SWCNT bundle, and diameter of SWCNT, respectively.

#### ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE)

## C. Capacitance of Bundled SWCNT Interconnect

The capacitance  $(C_b)$  of bundled SWCNT interconnect of length l is the series combination of its quantum capacitance  $(C_{qb})$  and electrostatic capacitance  $(C_{eb})$ . It can be expressed as [12-13]:

$$C_{b} = \frac{\left(C_{qb}.C_{eb}\right)l}{\left(C_{qb} + C_{eb}\right)} \tag{10}$$

Where  $C_{qb}$  and  $C_{eb}$  are *p.u.l* quantum capacitance and *p.u.l* electrostatic capacitance of bundled SWCNT interconnect, respectively. The *p.u.l* quantum capacitance ( $C_{qb}$ ) of SWCNT bundle is given by,

$$C_{qb} = C_q N_{CNT} \tag{11}$$

where  $C_q$  is the total *p.u.l* quantum capacitance due to of four parallel conducting channels of an isolated SWCNT and it can be expressed as,

$$C_q = 4C_{q-CNT} \tag{12}$$

where  $C_{q-CNT}$  is the *p.u.l* quantum capacitance of an individual isolated SWCNT and equal to  $2e^2/hV_F$ . Now, the *p.u.l* electrostatic capacitance ( $C_{eb}$ ) of SWCNT bundle can be expressed as [13]:

$$C_{eb} = 2.C_{en} + \frac{(N_w - 2)}{2}.C_{ef} + \frac{3.(N_T - 2)}{5}.C_{en} \quad (13)$$

where  $C_{en}$  and  $C_{ef}$  are the *p.u.l* electrostatic capacitances calculated assuming the ground plane to be at a distance equal to separation *S*, and (*S*+*W*) from the 'near' adjacent and 'far' adjacent interconnect, respectively. These capacitances can be expressed as [13]:

$$C_{en} = \frac{2\pi\varepsilon}{\ln(S/d)}^{(6)} \tag{14}$$

$$C_{ef} = \frac{2\pi\varepsilon}{\ln\left[\frac{(S+W)}{d}\right]}$$

(15)

#### III. SIMULATION SET UP

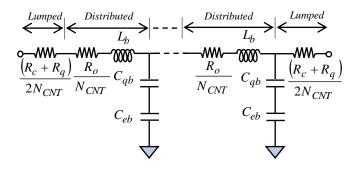

The parasitic resistance, inductance, and capacitance for bundled SWCNT interconnect are calculated by using the geometrical parameters and (3) to (15). The geometrical parameters used in simulations are obtained from the ITRS, as summarized in Table I at 32nm and 22nm technology nodes. The copper interconnect is modeled of the same geometrical structure and same dimensions as of bundled SWCNT interconnect. The predictive technology model is used to estimate interconnect parasitic elements for copper interconnect at same technology nodes. A typical schematic of driver-SWCNT/Cu interconnect-load (DIL) set up is used for the delay and power analysis, as shown in Fig. 3. In this Fig. 3,

# INTERNATIONAL JOURNAL OF RESEARCH IN ELECTRONICS AND COMPUTER ENGINEERING A UNIT OF I2OR 862 | P a g e

#### IJRECE VOL. 6 ISSUE 4 (OCTOBER-DECEMBER 2018)

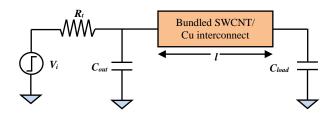

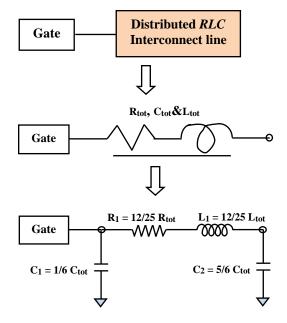

$R_t$  and  $C_{out}$  are the equivalent output resistance and capacitance of the gate driver, respectively, and  $C_{load}$  is the input capacitance of the load gate. The size of the driver and the load is to be assumed 100 times more than the minimum size gate for the global interconnects. The input excitation is assumed to be a ramp signal of 1V with clock frequency of 5 MHz. SPICE simulations are also carried out for copper interconnects of the same technologies and clock frequency. The pi ( $\pi$ )-equivalent distributed *RLC* circuit model proposed by Kahng and Muddu [14-15] is used for distributed *RLC* network of bundled SWCNT and Cu interconnect as shown in Fig. 4. (a) and (b). A simple approximation of an *RLC* interconnect line is obtained by using  $\pi$ -model achieving better accuracy in estimating the propagation delay and average power consumption.

Fig. 3. Schematic of driver-bundled SWCNT/Cu Interconnect-load model [12]

|                            | Parameters                                                       | Values<br>at 32nm<br>node | Values<br>at 22nm<br>node |

|----------------------------|------------------------------------------------------------------|---------------------------|---------------------------|

| Global<br>Interconnects    | Width of SWCNT bundle (W)                                        | 48 nm                     | 32 nm                     |

|                            | Spacing between adjacent<br>SWCNT bundles (S)                    | 48 nm                     | 32 nm                     |

|                            | Thickness of SWCNT<br>bundle ( <i>T</i> )                        | 144 nm                    | 96 nm                     |

|                            | Height from the ground plane<br>to the SWCNT bundle ( <i>H</i> ) | 144 nm                    | 96 nm                     |

|                            | Aspect ratio (A/R)                                               | 3                         | 3                         |

|                            | Diameter of SWCNT (d)                                            | 1 nm                      | 1 nm                      |

| Minimum                    | $R_t$                                                            | 13.85kΩ                   | 16.67kΩ                   |

| size of the<br>gate driver | $C_{out}$                                                        | 0.07 fF                   | 0.049 fF                  |

| gute arriver               | $C_{load}$                                                       | 0.25 fF                   | 0.14 fF                   |

| Relative<br>permittivity   | € <sub>r</sub>                                                   | 2.25                      | 2.05                      |

Table I: Structural parameters for bundled SWCNT interconnects [17]

Fig. 4. (a) Distributed *RLC* interconnect line modeled from N-segment *RLC* Circuit [15]

The  $\pi$ -model becomes more accurate as the resistance, inductance, and capacitance of the distributed *RLC* line

increases [16]. The propagation delay and average power consumption for bundled SWCNT interconnect is estimated by running the SPICE simulations and compared with the traditional copper interconnect.

Fig. 4. (b) An open-ended *RLC* line to capture an *RLC* interconnect line, and the *RLC*  $\pi$  model [15]

# **IV.SPICE SIMULATION RESULTS**

This section describes and analyzes the effect of driver size on propagation delay and power consumption for different lengths of bundled SWCNT interconnects at global level.

#### A. Delay Analysis

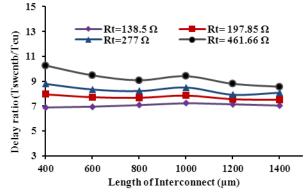

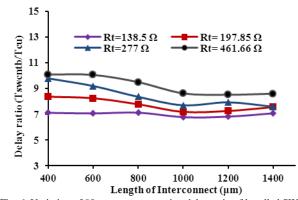

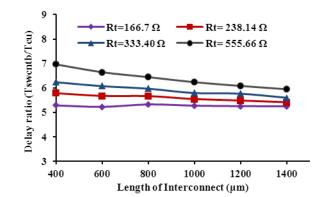

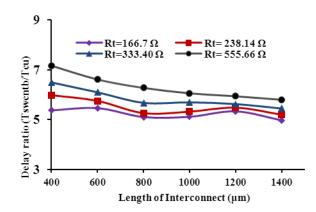

The 50 and 90 percent propagation delays for both bundled SWCNT and copper interconnect are obtained at 32nm and 22nm technology nodes by running the SPICE simulations. The length of interconnect is varied from 400 $\mu$ m to 1400 $\mu$ m which lies in global interconnect range. The delay ratio of bundled SWCNT to copper interconnects is evaluated and analyzed at both technology nodes for both cases. Figs. 5, and 6; and Figs. 7 and 8 demonstrated the delay ratio between the bundled SWCNT interconnects to the copper interconnects by varying the driver size at 32nm and 22nm technology node, respectively.

From Figs. 5, and 6; and Figs. 7, and 8, it is observed that both 50 percent, and 90 percent propagation delay ratio  $(T_{swentb}/T_{Cu})$ , respectively, decreases with increase in length of interconnect for various driver sizes (variation in driver resistance and input capacitance of the load gate) at 32nm and 22nm technology nodes. Further, it is also observed that the propagation delay ratio increases with increase in driver size for both the cases at both technology nodes. Fig. 6 demonstrates the 90 percent propagation delay ratio which is less than the 50 percent delay ratio shown in Fig. 5, with respect to the variation of driver sizes at 32nm technology node. Moreover, it is observed that the 50 percent propagation

#### IJRECE VOL. 6 ISSUE 4 (OCTOBER-DECEMBER 2018)

delay ratio shown in Fig. 7 is less than the 90 percent propagation delay ratio as in Fig. 8, at 22nm technology nodes. Due to the reduced feature size and scaled down of structural parameters of bundled SWCNT and copper interconnects, it is observed that the propagation delay ratio obtained at 22nm technology node is less than the propagation delay ratio at 32nm technology node for both cases. Therefore, the propagation delay ratio obtained at 22nm technology node is the better choice to minimize the delay for interconnects designers. Thus, it can be very well inferred that the bundled SWCNT interconnects would be more appropriate than copper to minimize the delay for global interconnects in near future.

Fig. 5. Variation of 50 percent propagation delay ratio of bundled SWCNT to Cu, versus length of global interconnect with different driver sizes at 32nm technology node

Fig. 6. Variation of 90 percent propagation delay ratio of bundled SWCNT to Cu, versus length of global interconnect with different driver sizes at 32nm technology node

ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE)

Fig. 7. Variation of 50 percent propagation delay ratio of bundled SWCNT to Cu, versus length of global interconnect with different driver sizes at 22nm technology node

Fig. 8. Variation of 90 percent propagation delay ratio of bundled SWCNT to Cu, versus length of global interconnect with different driver sizes at 22nm technology node

# B. Power Analysis

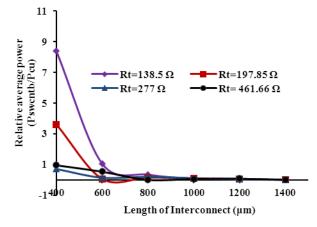

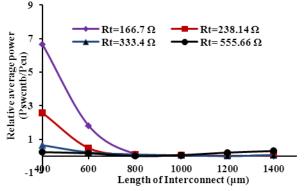

The average power consumption for both bundled SWCNT and copper wire interconnect is obtained by running the SPICE simulations at 32nm and 22nm technology nodes for the same global length of interconnect.

A ratio of bundled SWCNT and Cu interconnects; the average power consumption is evaluated and analyzed by varying the driver size at both technology nodes. This ratio of average power consumption is referred to as "relative average power consumption." From Figs. 9, and 10, it is observed that the ratio of the relative average power ( $P_{swentb}/P_{Cu}$ ) is decreasing with increase in length of interconnect, and varying the driver sizes for both technology nodes at global level. However, the ratio of relative power consumption is higher for minimum driver size and lesser for maximum driver size at both 32 and 22nm technology nodes. Thus the ratio of relative average power consumption is reducing with increasing the driver size.

Fig. 9. Variation of relative average power consumption of bundled SWCNT to Cu versus length of global interconnects with different driver size at 32nm technology node

Fig. 10. Variation of relative average power consumption of bundled SWCNT to Cu versus length of global interconnects with different driver size at 22nm technology node.

## V. CONCLUSION

This paper analyzed the effect of driver size on propagation delay and average power consumption for bundled SWCNT interconnects at 32nm and 22nm technology nodes. An equivalent circuit model of bundled SWCNT is chosen for the estimation and analysis of propagation delay and power consumption for global length of interconnects. The pi ( $\pi$ ) equivalent distributed *RLC* circuit model is applied for bundled SWCNT and Cu interconnects to analyze the delay and power by varying the driver sizes. The delay ratio, and ratio of average power consumption of bundled SWCNT to Cu interconnects are obtained by running the SPICE simulations for various driver sizes at both technology nodes. It is observed that the propagation delay ratio is decreasing with increase in length of interconnect and it is minimum for smallest value of driver size for both technology nodes. Moreover, the propagation delay ratio obtained at 22nm technology node is less than the delay ratio at 32nm technology node for same length of interconnects. Furthermore, the ratio of average power consumption is decreasing with increase in length of interconnect and it is minimum between 800µm to 1000µm length of interconnect for higher value of driver size at both technology nodes. Therefore, it can be concluded that the propagation delay ratio

## ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE)

is lesser for smallest value of driver size, and the ratio of average power consumption is lowest at 22nm technology node as compared with 32nm technology node.

# REFERENCES

- [1] W. Steinhögl, G. Schindler, G. Steinlesberger, and M. Engelhardt, "Size dependent resistivity of metallic wires in the mesoscopic range," Physical Review B, Condensed Matter and Materials Physics, vol. 66, no. 7, pp. 075414-1-075414-4, August 2002.

- [2] N. Srivastava, and K. Banerjee, "A comparative scaling analysis of metallic and carbon nanotube interconnections for nanometre scale VLSI technologies," Proceedings of the 21<sup>st</sup> International VLSI Multilevel Interconnect Conference, pp. 393-398, Sept. 29-Oct. 2, 2004.

- [3] F. Kreupl, A. P. Graham, G. S. Duesberg, W. Steinhögl, M. Liebau, E. Unger, W. Hönlein, "Carbon nanotubes in interconnect applications," Microelectronic Engineering, vol. 64, no. 1- 4, pp. 399-408, October 2002.

- [4] A. Naeemi, and J. D. Meindl, "Design and performance modeling for single-walled carbon nanotubes as local, semiglobal, and global interconnects in gigascale integrated systems," IEEE Trans. on Electron Devices, vol. 54, no. 1, pp. 26–37, January 2007.

- [5] P. L. McEuen, M. S. Fuhrer, and H. K. Park, "Single-walled carbon nanotube electronics," IEEE Trans. on Nanotechnology, vol. 1, no. 1, pp. 78–85, March 2002.

- [6] P. L. McEuen, and J. Y. Park, "Electron transport in singlewalled carbon nanotubes," Materials Research Society Bulletin, vol. 29, no. 4, pp. 272-275, April 2004.

- [7] J. Li, Q. Ye, A. Cassell, H. T. Ng, R. Stevens, J. Han, and M. Meyyappan, "Bottom-up approach for carbon nanotube interconnects," Applied Physics Letters, vol. 82, no. 15, pp. 2491–2493, April 2003.

- [8] A. Raychowdhury, and K. Roy, "A circuit model for carbon nanotube interconnects: comparative study with Cu interconnects for scaled technologies," IEEE/ACM International Conference on Computer-Aided Design, pp. 237-240, November 2004.

- [9] A. Raychowdhury, and K. Roy, "Modeling of metallic carbonnanotube interconnects for circuit simulations and a comparison with Cu interconnects for scaled technologies," IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems, vol. 25, no.1, pp. 58-65, January 2006.

- [10] A. Naeemi, R. Sarvari, and J. D. Meindl, "Performance comparison between carbon nanotube and copper interconnects for GSI," International Electron Devices Meeting Technical Digest, pp. 699-702, December 2004.

- [11] A. Naeemi, R. Sarvari, and J. D. Meindl, "Performance comparison between carbon nanotube and copper interconnects for gigascale integration (GSI)," IEEE Electron Device Letters, vol. 26, no. 2, pp. 84-86, February 2005.

- [12] N. Srivastava, H. Li, F. Kreupl, and K. Banerjee, "On the applicability of single-walled carbon nanotubes as VLSI

# INTERNATIONAL JOURNAL OF RESEARCH IN ELECTRONICS AND COMPUTER ENGINEERING A UNIT OF I2OR 865 | P a g e

interconnects," IEEE Trans. on Nanotechnology, vol. 8, no. 4, pp. 542–559, July 2009.

- [13] N. Srivastava and K. Banerjee, "Performance analysis of carbon nanotube interconnects for VLSI applications," in Proceedings of IEEE/ACM International Conference, pp. 383– 390, November 2005.

- [14] A. B. Kahng and S. Muddu, "Efficient gate delay modeling for large interconnect loads," IEEE Multi-Chip Module Conference, pp. 202–207, February 1996.

- [15] A. B. Kahng and S. Muddu, "An analytical delay model for *RLC* interconnects," IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems, vol. 16, no. 12, pp. 1507-1514, December 1997.

- [16] B. K. Kaushik, S. Sarkar, and R. P. Agarwal, "Waveform analysis and delay prediction for a CMOS gate driving *RLC* interconnect load," Integration, the VLSI Journal, vol. 40, no. 4, pp. 394-405, July 2007.

- [17] International Technology Roadmap for Semiconductors, 2005 Edition, 'Interconnect'. available at: http://public.itrs.net.

Yograj Singh Duksh has received his M.Sc. degree in Physics with Electronics from Rohilkhand University, Bareilly, in 1996, M. Phil Degree in Instrumentation from University of Roorkee, Roorkee in 1999, M. Tech. Degree in Instrumentation from National Institute of Technology, Kurukshetra in 2001 and Ph.D

Degree in Electronics Engineering from Shobhit University, Modipuram, Meerut in 2016 respectively. He has approximate seventeen years of teaching experience in various Institutions. Presently, He is working as Associate Professor in the Department of Electronics and Instrumentation Engineering, Faculty of Engineering and Technology, Mahatma Jyotiba Phuley Rohilkhand University, Bareilly from 2008 to till date. His research area is Delay and Crosstalk Modeling of Carbon Nanotube based VLSI Interconnects.