# Study of Development in Xilinx System Generator Tool Implementation of Real Time 2-D Images

P.Alamelu<sup>1</sup>, G.Nirmala<sup>2</sup>, V.Soundappan<sup>3</sup>

<sup>1</sup>AVS Engineering College, Salem, Tamil Nadu, India

<sup>2&3</sup> Mahendra Institute of Technology, Namakkal, Tamil Nadu, India

(alamsshanthi@gmail.com, g.s.nila@gmail.com, soundappanv@mahendratech.org)

Abstract— Edge detection is required tool for removal of information for additional image processing operation. a lot of computer vision application utilize edge detectors as main operators previous to high level image processing. quite a lot of algorithms are on hand for edge detection which makes use of derivative approach. Roberts, Prewitt, sobel, canny are some of the examples of edge detection methods. In this manuscript edge detection algorithms are to be implemented over FPGA board. Proposed architecture gives an alternative by using a graphical user interface which is urbanized by combining MATLAB, Simulink and XSG tool. Prototype of Application Specific Integrated Circuit can be obtained by FPGA based implementation of edge detection algorithm. Comparative analysis using software and hardware is to be done. Instead of using traditional approach of programming FPGA, Xilinx System Generator is used for programming and modeling FPGA. XSG has an integrated design flow to move directly to the bit stream file from simulink design situation which is necessary for programming the FPGA. Benefit of using FPGA is power proficient circuits can be made-up; it has large memory and superior parallel computing capacity. With use of FPGA, design procedure becomes more flexible.

**Keywords**— ASIC, FPGA, MATLAB ,Prewitt, Sobel, XSG Introduction

## I. INTRODUCTION

Edge detection is an necessary preprocessing step in image processing. Edge detection is a place of mathematical rules with identifies the point in a digital image wherever the brightness of image sharply changes or has discontinuities. The need to find the sharp modification in an image is to capture all the significant event and property changes. In a lot of applications it is required to find boundaries of objects that appear in images.

Edge detection is always one of the traditional studying projects of computer vision and image processing field. It is the first step of image analysis and understanding. The purpose of edge detection is to discover the in order about the shapes and the reflectance or transmittance in an image. The rightness and dependability of its results involve directly the comprehension machine system made for objective world. Low level image processing operations like image segmentation using edge detection and feature extraction helps us to analyze, infer and take result in various applications. It focuses on processing an image pixel by pixel and over its locality. Image processing operations can be applied to the whole image or its parts.

The edge is characterized by its length, slope angle, and coordinate of the slope midpoint. amongst several ways for performing edge detection; the bulk may be grouped into two categories, Gradient and Laplacian based approach.

The basic Edge detection operator is a matrix area gradient operator that determines the level of variance between different pixels. It is designed by forming a matrix centered on a pixel selected as the centre of the matrix area. If the value of the matrix area is above 2 a given threshold, then the center pixel is classified as an edge. Examples of gradient based edge detectors are Roberts, Prewitt and Sobel operators. All the gradient based algorithms have Kernel operators that calculate the power of the slope in directions that are orthogonal to each other, generally horizontal and vertical Clasically, Edge detection algorithms have been implemented over software plat-form.

With progression in the VLSI technology hardware implementation has become an attractive option. Assigning complex computation tasks to hardware and exploiting the parallelism and pipelining features yield significant speedup in running times. Implementation of image processing on reconfigurable hardware, enables rapid prototyping of algorithm and simplifies debugging complex and verification. In recent years FPGAs (Field Programmable Gate Array) have become superior platform, with high-speed parallel computing capacity. FPGA is a fine grained device with large number of Input Output Blocks (IOBs) and Configurable Logic Block (CLBs) and other logic elements. FPGA is rich source of high speed multipliers, adder, and memory; in the design process they can be directly called. next it is easy to implement complex convolution over this stand. FPGA based design offers an advantage of short Turn Around Time (TAT) and small Non Recurrent Expense (NRE). While implementing an algorithm over hardware platform, in the traditional approach, user needs to emulate the floating point algorithm in HDL code. Further, it be able to be tested and verified by repeated functional simulations, post

simulation processes and finally generate bit stream file. Xilinx introduces the system modeling tool Xilinx System Generator.

# **II EDGE DETECTION**

Edge detection is one of the most normally used operations in image analysis, and there are probably more algorithms in literature for enhancing and detecting edges. An edge is point of sharp change in an image, a region where pixel locations have abrupt luminance change i.e. a discontinuity in gray level values. In other words, an edge is the boundary between an object and the background. The shape of edges in images depends on many parameters like the depth discontinuity, surface orientation discontinuity, reflectance discontinuity, illumination discontinuity, and noise level in the images.

#### A.The major steps in edge detection

1.Filtering: It is gradient addition based on intensity values of two points which are susceptible to noise. Filtering reduces noise but there is a trade- off between edge strength and noise reduction.

2.Enhancement: It is done in order to facilitate the detection of edges, it is important to determine intensity changes in the neighborhood of a pixel in an improved manner. Enhancement emphasizes pixels where there is a major change in local intensity values and is usually performed by computing the gradient magnitude

3.Detection: It is done since many points in an image have a nonzero value for the gradient, but not all these points can be measured to be edges. Therefore, some method should be used to determine which points are edge points. Frequently, threshold provides the criterion for detection.

4. Prewitts edge detection algorithm: The Prewitt operator is based on the idea of central difference and is much better than Roberts's operator. It is based on convolving the image with a small, separable, and integer valued filter in horizontal and vertical direction as exposed in equation.

#### **III RELATED WORK**

An general work is done in the field of edge detection for real time image processing. In recent years, in September 2009[8] the algorithm implementation for FPGA based design for various applications using edge detection was proposed. The hardware processing on an FPGA allows the capture and online processing in real time on the same chip. External memory module can be saved using memory from FPGA only. The rate achieved by PC is greater than FPGA because PC clock is much higher than FPGA. In another paper improvement was done by using block RAM and IO interface on the FPGA. After this in 2010 the improvement was done by implementing the hardware circuit of the algorithm on ISE 9.1 and simulated in Model sim 6.0.

It gave high precision edge. When the system is validated, it indicates that the video image edge detection system can detect high precision edge. This paper realizes hardware based video edge detection system on FPGA mainly by the completion of the system IP core. Next stage was achieved by using A Moving Window Architecture in MAY 2012[5] which performs the more computational complex operations of edge detection algorithm like non maximum suppression and double thresholding By using this design results are stored within the FPGA and eliminates the needs of large memory buffer. The proposed architecture in this manuscript are providing a platform for real time alforithm on application exact hardwre with higher performance than programmable digital signal processors. In 2011 edge detection algorithm for prewitt and sobel was accessible and compared their result. After that A methodology for real time architecture designed for Edge detection using sobel filter for image processing using Xilinx System Generator. In this approach a Virtex 5 FPGA kit is used to achieve higher presentation than previous methods. In 2013 Paulo possa existing a new flexible architecture for image and video processing with reduced latency and memory food behind a variable input resolution. The proposed architecture is optimized for feature extraction such as the canny edge detector and the Harris corner detector. Also algorithm simplifications are employed to reduce mathematical implementations on an FPGA based modules. It has clear advantage in low level power applications, low latency and portability are necessary.

#### IV PROPOSED WORK

The aim of our project is to implement various edge detection algorithms via FPGA kit.

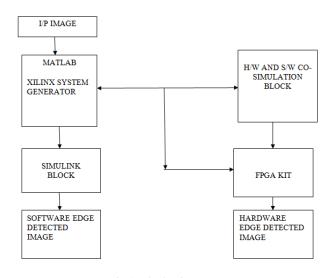

Fig 1. Block Diagram A.Software implementation:

1. Initially the original digital image which may be color is firstconverted into Grey scale image using MATLAB.

2.This 2-D image is then rehabilitated into 1-D for further processing. This 1-D data stream is given to Frame conversion block.

INTERNATIONAL JOURNAL OF RESEARCH IN ELECTRONICS AND COMPUTER ENGINEERING

176 | Page

3.At this point edge detection using XSG is done. This is followed by arithmetic blocks to combine all processed data.

4.The 1-D output of XSG block set are given to image post processing blocks to obtain original 2-D image with its edge detected.

Fig 4. A.Orginal Image

b.Prewitt

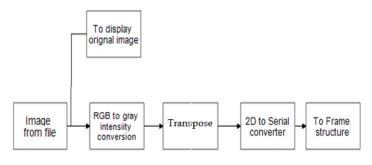

For the design of filters to meet hardware requirements, it is a must to pre-process the image prior to the major hardware architecture. In the software level simulation using Simulink block sets alone, where the picture is used as a two- dimensional(2D) arrangement such as  $M \times N$ , there is no need for any image pre-processing, but at hardware level this matrix must be an array of one dimension(1D), namely a vector, where it requires image pre-processing. Image Pre- processing Block sets

Fig 2. Image Pre- processing Block

The model based design used for image preprocessing is shown. The blocks utilized here are discussed below. Input images which could be color or grayscale are provided as input to the File block. A color space adaptation block converts RGB to grayscale image and this data which is in 2D is to be converted to 1D for extra processing. Frame conversion block sets production signal to frame base data and provided to unbuffer block which converts this frame to scalar samples output at a higher sampling rate.

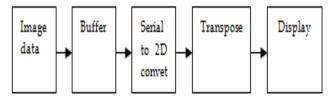

The image post-processing blocks which are used to convert the image output back to floating point type.

Fig 3. For post-processing

For post-processing it uses a Buffer block which changes scalar samples to frame output at lower sampling rate, followed by a 1D to 2D (matrix) format signal block, finally a sink is used to display the output image back in the monitor, utilizing the Simulink block sets.

## V CONCLUSION

Real time applications are always on hardware platform rather than software. In this paper short level digital image processing technique which is edge detection algorithm larger than software and hardware platform is proposed. a number of edge detection algorithms are available But we are implementing them on hardware platform using Xilinx system generator tool. XSG tool of MATLAB provides simpler and proficient way of FPGA programming.

#### REFERENCES

[1] Jiang, R. M. and D. Crookes, \FPGA implementation of 3D discrete wavelet transform for real-time medical imaging," ECCTD, 519{522, August 2007.

[2] J. A. Parker, R. V. Kenyon, and D. E.Troxel, "Comparision of interpolation methods for image resampling," IEEE Trans. Med. Imag., vol.MI-2, no. 3, pp. 31–39, Sep. 1983.

[3] B.E. Shi and L.O chun ,"Resistive grid image filtering:Input/output analysis via the CNN framework," IEEE Trans.circuits syst. I,vol. 39,no. 7,pp. 531-548,Jul .1992.

[4]. Sweldens, W., \The lifting scheme: A customdesign construction of biorthogonal wavelets," Applied and Computational Harmonic Analysis, Vol. 3, No. 2, 186{200, Article No. 15, April 1996.

[5]. Daubechies, I. and W. Sweldens, \Factoring wavelet transforms into lifting steps," Journal of Fourier Analysis and Applications, Vol. 4, No. 3, 247{269, 1998.

[6]. Sweldens, W., \The lifting scheme: A construction of second generation wavelets," SIAM Journal on Mathematical Analysis, Vol. 29, No. 2, 511{546, March 1998.

[7]. Spiliotopoulos, V., N. D. Zervas, C. E. Androulidakis, G. Anagnostopoulos, and S. Theoharis,\Quantizing the 9/7 daubechies <sup>-</sup>lters coe±cients for 2D DWT VLSI implementions," Digital Signal Processing, Vol. 1, 227{231, 2002.

[8] Xiong, C., S. Zheng, J. Tian, and J. Liu, \The improved lifting scheme and novel recon<sup>-</sup>gurable vlsi architecture for the 5/3 and 9/7 wavelers,"