# A Review Paper on CNTFET Technology and Circuit Designing using CNTFET

Manoj Kumar<sup>1</sup>, Shikha Verma<sup>2</sup> <sup>1</sup>M.tech Scholar, <sup>2</sup>Assistant Professor ECE, L.R.I.E.T, Solan, Himachal Pradesh, India.

Abstract - In this review paper we study on circuit based on CNTFET and its advantages of use in adders and logical circuits using multi logic and conventional logic also use of ternary logic is discussed. The utilization of carbon nanotube field effect transistors (CNFETs) for the plan of ternary full snake cells. These days, numerous examinations are continuing for planning and investigating the use of CNTFETs in logic gates and benchmarking their execution leverage over the current MOS innovation. The CNTFET circuit application incorporates parallel logic gates, ternary logic gate, ternary and paired memory cells and numerous esteemed logics. The utilization of CNTFETs for various esteemed logic has increased unmistakable fascination as the edge voltage of CNTFETs can be constrained by legitimate choice of the chiral vector of the CNT (carbon nano tube). Logic circuits just as various adders, multipliers and recollections are additionally intended to get less deferral, lower power utilization and to have decreased interconnection intricacy. Right now on-chip interconnections have turned into a genuine test as an ever increasing number of modules are pressed into a chip. In a normal twofold circuit chip, a greater amount of the zone is involved by interconnects, 20% for protection and 10% for transistors. These interconnects scatter bunches of vitality, increment reaction time, and cause coupling effects by including more capacitance, opposition, and inductance to a circuit.

*Keywords* - carbon nanotube field effect transistors (CNFETs), logic gates, MOS technology, binary logic gates, ternary logic gates, adder, multipliers.

## I. INTRODUCTION

Because of the constraints of CMOS transistors, they are not ready to proceed with the procedure of highlight measure decrease and ought to be supplanted by new option developing advances. CMOS transistors have issues, for example, short channel effect, decreased gate control, high leakage power and parameter variety. Along these lines, considering elective new advancements, for example, Quantum dab Cellular Automata (QCA), Single Electron Transistors (SET) and Carbon Nanotube Field-Effect Transistors (CNFET) [4] is basic. A reasonable option for CMOS transistors is CNFET. In view of the similitudes among CMOS and CNFET transistors regarding natural electronic parameters, CNFET could be a decent elective innovation with no significant changes in CMOS stages. Moreover, a novel normal for CNFET gadgets is one dimensional band structure which stifles backscattering and causes close ballistic activity, that makes it reasonable for executing quick and low power CNFET based circuits [4]. Another element of CNFET is that it has same portability and thus same current drive for P-FET and N-FET gadgets. This makes transistor estimating simpler for complex circuits. Among all uses of CNFET transistors, Multiple Valued Logic (MVL) could be a greater amount of an intrigue. MVL logic implies utilizing in excess of two logic esteems for planning circuits and frameworks. Utilizing CNFETs is fitting for MVL structuring. Since MVL depends on numerous limit plan method and deciding the edge voltage of CNFETs is effectively conceivable by changing the measurement of the nanotubes. One of the significant difficulties of paired logic is the quantity of stick includes and interconnects uncommonly in thick chips. This issue constrains the quantity of inside and outside associations. By utilizing MVL, we can diminish the circuit territory by lessening the overhead in interconnects and stick tallies. In MVL plans, wires and interconnections convey more data than paired logic; along these lines, it has higher speed and more modest number of calculation stages [6]. Among all radices that exist for MVL logic,  $e \approx 2.718$ ) base tasks have the most proficient usage [8]. Be that as it may, because of the equipment confinements for actualizing genuine frameworks, we should utilize characteristic numbers as the base of calculations. Thus, radix 3 which is the closest normal number to e; is progressively alluring ternary logic is the best and prompts less unpredictability and generation cost.

## II. LITERATURE REVIEW

A large piece of the achievement of the MOS transistor is because of its adaptability to a lot littler measurements, which is better execution. This pattern still proceeds as per Moore's law, and silicon-based innovation has experienced an extraordinary development over the most recent couple of decades. Be that as it may, as MOSFETs are moving toward their constraining size in the nanometer routine, the semiconductor business is searching for various materials and elective gadgets to incorporate with the ebb and flow silicon-based innovation and, over the long haul, perhaps supplant it [1]. Carbon Nano Tube Field Effect Transistors (CNFET) are framed in the state of a sheet of graphite tubes. A few points of interest of CNFETs are, for example, they have higher ON current contrasted with MOSFET transistors. By utilizing CNFETs it is conceivable to scale down element estimate, past what as of now lithographic

#### IJRECE VOL. 7 ISSUE 2 APR.-JUNE 2019

strategies grant. Additionally, ballistic conduction of CNFETs lessens the power dissipation in the transistor body. One-measurement structure of CNTs lessens the resistivity and therefore the vitality dissipation and power utilization [2]. Full Adder is the fundamental component for number juggling tasks utilized in Very Large Scale Integrated (VLSI) circuits, in this manner, advancement of 1-bit full snake cell improves the general execution of electronic gadgets. Because of interesting mechanical and electrical attributes, carbon nanotube field effect transistors (CNTFET) are observed to be the most reasonable option for metal oxide field effect transistor (MOSFET). CNTFET transistor uses carbon nanotube (CNT) in the channel district. In this paper, rapid, low power and diminished transistor tally full viper cell utilizing CNTFET 32nm innovation is exhibited [3]. This structure work has been having been instated with the customary way to deal with build the viper cell with CNTFET adders having complimentary draw up PCNTFET and draw down NCNTFET systems. This snake required 42 transistors for producing aggregate and convey yields. An elective viper configuration utilizing XOR logic and transmission gate is additionally investigated in which the transistor check is diminished to 30 when we construct transistor level XOR gates to achieve adders [4]. The structures of essential ternary gates/administrators (inverters, NAND, and NOR) are depicted in detail, and ternary full viper, and multiplier plans and investigation are exhibited as instances of the utilization of these ternary gates plan procedure. For the math circuit structure, a changed ternary logic circuit plan procedure is utilized to accelerate and decrease power utilization of the circuits. The altered ternary logic configuration utilizes both ternary logic gates and double logic gates dependent on the past ternary logic configuration structures to exploit the two logic configuration styles' benefits. The ternary logic gates are a decent possibility for disentangling hinder since it requires less number of gates while paired logic gates are a decent contender for quick calculation [5]. Ternary logic has numerous favorable circumstances over double circuits, for example, it diminishes the quantity of required calculation steps. The Full snake displayed in this paper depends on ternary logic. The circuit structured in this paper has low limit voltage to keep the power dissipation low. Pseudo N-type CNTFET's is utilized to structure the TFA cell. The full viper is planned dependent on twofold nature of a TFA and pseudo transistor-based logic requiring less gates. To diminish the power utilization the structure utilizes two sources [6].

#### **III. CNTFET STRUCTURE**

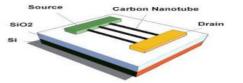

Figure 1: CNTFET structure similar to that of a MOSFET

#### ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE)

With the progression of innovation requirement for littler superior electronic gadgets are developing quickly. Downsizing of MOSFET transistors has achieved its base and further contracting has presented difficulties like high leakage current, uninvolved power dissipation, short direct effects and varieties in gadget structure and doping. These difficulties can be defeated to a very decent degree by supplanting the customary MOSFET with Carbon nano tube field effect transistors. Basically CNTFET is like MOSFET, with carbon nano tubes utilized as channels rather than customary channel material. Considering the upsides of CNTFETs a great deal of twofold, multi esteem logic, number juggling circuits have been planned [6]. Carbon Nanotube Field Effect Transistor (CNTFET) is one of the developing components of nanoelectronics that has the preferable execution over all the best in class rising innovation. Nanotechnology is another field of research that cuts crosswise over numerous fields - gadgets, science, material science, and science, that breaks down and blends objects and stnictures in the nano scale (10-9 m)such as nanoparticles, nanowires, and Carbon Nano-Tubes (CNTs). CNT is one of the few bleeding edge rising advancements inside nanotechnology that is demonstrating high effectiveness and very wide scope of innovation. Instances of such applications are: TVs dependent on field-discharge of CNTs that expend considerably less power, more slender, and a lot higher goals than the best plasma-based TV accessible, and nanocircuits dependent on CNTs, for example, CNT Field Effect Transistors (CNTFETs) that show enormous guarantee of devouring less power and to be a lot quicker than the accessible silicon based FETs[7]. CNTFET-based ternary logic gates and combinational circuits configuration is exhibited so as to improve the Power Delay Product (PDP). Advanced frameworks that are quick and have low power necessity are planned and contrasted and the current structures. The general target of this paper is to structure logic gates and combinational circuits with diminished Power Delay Product (PDP). The PDP is the result of the normal power devoured and the normal postponement happened amid spread of the signs through the combinational circuits. In this manner, it is one of the execution estimations in VLSI advanced framework plan [8]. Various Valued logic (MVL, for example, Ternary logic is considered over paired logic because of its significant points of interest, for example, diminished interconnects, chip region [3], quicker sequential, sequential parallel number juggling tasks. MVL logic improves the execution of CMOS innovation in the logic structure.

INTERNATIONAL JOURNAL OF RESEARCH IN ELECTRONICS AND COMPUTER ENGINEERING A UNIT OF I2OR 1663 | P a g e

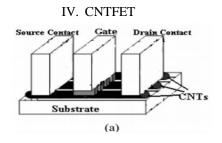

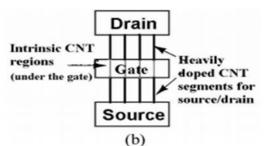

Figure 2: CNTFET (a) Schematic diagram (b) Top view

Single walled CNT (SWCNT) is made by folding graphene sheet into barrel shaped shape with the goal that the structure is one-dimensional. SWCNT is utilized to structure gadgets [8] in CNTFETs. CNT has magnificent compound, mechanical, electrical property. The concoction bond in CNT comprises of sp2 which gives it compound quality. CNT is a decent option since it gives transporter transportation in one-dimensional in this manner smothering the dispersing effect and furthermore it has low power dissipation. SWCNTs electrical property can be either metallic or semiconducting relying upon its chirality. Chirality (n, m) is chosen by the chiral point at which graphene sheets are moved [9]. The option for the CMOS innovation is the CNTFET. The closeness among CMOS and CNTFET in a gadget structure and standard task, we can acquire the required CMOS assembling and CMOS plan in the CNTFET innovation. A portion of the significant attributes of CNT are: high ION/IOFF proportion, the special measurement band which stifles back dissipating. Contrasting CNTFET and MOSFET, MOSFET have greater adaptability and less size which makes them progressively reasonable for uprooting. Because of the phenomenal electric properties of CNTFET, the CNTFET are alluring for the nano electronic applications. The CNT's are high impervious to electro movement on the grounds that the structure of a band is immediate in which it empowers the optical discharge. A considerable lot of the endeavors has been done to comprehend that how a CNT works and how to improve the execution of transistor [10]. To ease these challenges, some past MOS nano devices, for example, Carbon Nanotube Field Effect Transistor (CNTFET), Single Electron Transistor (SET), Graphene Nanoribbon Transistor (GNRT) and Quantum-spot Cellular Automata (QCA), the potential choices to supplant the ordinary mass CMOS sooner rather than later [1]. In any case, thinking about these nano devices, CNTFET could be a greater amount of an enthusiasm because of its similitudes with MOSFET regarding intrinsic electronic properties [11].

### V. CONCLUSION

Hence in this review paper we studied CNTFET and its advantages of use in adders and logical circuits using multi logic and conventional logic also use of ternary logic is discussed.in this theoretically having many advantages like Area, delay, low power, noise immunity. Ternary logic is a promising alternative to the conventional binary logic in

### ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE)

VLSI design as it provides the advantages of reduced interconnects, higher operating speeds, and smaller chip area and the Ternary logic is a promising alternative to conventional binary logic, since it is possible to accomplish simplicity and energy efficiency in modern digital design due to reduced circuit overhead such as interconnect and chip area.

#### VI. REFERENCE

- [1]. Subhendu Kumar Sahoo et al., "High Performance Ternary Adder using CNTFET" 1536-125X (c) 2016 IEEE

- [2]. Fazel Sharifi et al., "High Performance CNFET-based Ternary Full Adders" IEEE, vol. 91, no. 2, pp. 305-327, 2003.

- [3]. Priya Kaushal et al., "Energy Efficient CNTFET Based Full Adder Using Hybrid Logic" IJRITCC | July 2017

- [4]. Balaji Ramakrishna S et al., "CNTFET Based Novel 14T Adder Cell for Low Power Computation" ICTACT Journal on Microelectronics, October 2017, Volume: 03, Issue: 03

- [5]. Sheng Lin et al., "CNTFET-Based Design of Ternary Logic Gates and Arithmetic Circuits" IEEE TRANSACTIONS ON NANOTECHNOLOGY, VOL. 10, NO. 2, MARCH 2011

- [6]. Kazi Muhammad Jameel et al., "Experimental Design of a Ternary Full Adder using Pseudo N-type Carbon Nano tube FETs" Volume: 02 Issue: 09 | Dec-2015

- [7]. SeyyedAshkanEbrahimi et al., "Low Power CNTFET- Based Ternary Full Adder Cell for Nanoelectronics" ISSN: 2231-2307, Volume-2, Issue-2, May 2012

- [8]. Mohsen Chegin et al., "Carbon Nanotube Field Effect Transistor-Based Combinational Circuits" GMP Review, 2015; V16(3)

- [9]. Gaurav Agarwal et al., "Performance Evaluation of CNTFET Based Ternary Basic Gates and Half Adder" Volume 5 Issue 5, May 2016

- [10]. Manjunath Patil et al., "Power Efficient Parallel Adder Design Using CNTFET Technology" IJEEE Volume 2, Issue 4, April 2015

- [11]. Mohammad Hossein Moaiyeri et al., "Efficient CNTFETbased Ternary Full Adder Cells for Nanoelectronics" Received 27 Feb 2011; accepted 11 April 2011; published online 19 April 2011