# EFFICIENT MICROPROCESSORS FOR POWER BINNING WITH NEW SCHEMES

\* B PRAVEENA, \*\*Dr TOWHEED SULTANA

\*MTech student, Dept of ECE, JBIET, Hyderabad, TS, India.

\*\* Professor, Dept of ECE, JBIET, Hyderabad, TS, India.

ABSTRACT - The substantial method guideline variants developing in the course of manufacture from quality consecutive circuits, including microprocessors, are actually presenting appropriate unpredictability's on the energy that such circuits are going to eat in the business, while implementing amount of work normal for the unique items they are actually divined. A brand new strategy for exam style creation in an integrated self-test atmosphere is actually designed right here. The TPG makes use of the unique details from the circuit to produce the examination angles inside. In this particular suggested technique for lowering the unnecessary time clock sign utilizing locks complimentary time clock gating methods. Time clock gating modern technology may lower the usage from time clock signs' shifting energy from flip-flops. The time clock gateway makes it possible for functionalities may be recognized through Boolean evaluation from the reasoning inputs for all vipers. Nevertheless, the permit functionalities from time clock gateway may be more streamlined, as well as the typical amount of vipers steered through make it possible for features could be boosted. This way, the circuit place may be lowered; for that reason, the time clock gating could be enhanced and also energy conserving may be obtained. Our technique manipulates scan-based Logic Built-In Self-Test to put on microprocessors' consecutive blocks exam angles that cause on their interior nodules a task aspect just like that experienced throughout the in-field completion from amount of work regular for other sort of items, therefore permitting to do electrical power binning through just assessing their eaten electrical power.

**Keywords:** Built In Self Test, Flip Flops, TPG, Clock signals, Boolean Analysis, Microprocessors.

## I. INTRODUCTION

Efficiency (or even velocity) binning pertains to evaluate operations to establish the max operating regularity from a CPU. This prevails technique to hasten can processor chips for classed prices. Therefore, also in the existence from producing procedure variant, processor chips may be created at the traditional "edges", unlike ASICs, which are actually developed at the worst-case sections. Binning a processor chip additionally establishes the desires for the customer concerning the efficiency that must be actually anticipated from the CPU potato chip. The energy that will certainly be actually taken in through microprocessors throughout the completion from traditional work-loads in the business must

be actually properly defined by the end from their assembly, to validate whether they could be used for a thought about type of items. Furthermore, the energy intake depiction by the end from manufacture might make a market chance for those microprocessors that, although certainly not fulfilling the electrical power restrictions for an offered sort of items, might in-deed be actually worked with for a various particle from the market place, along with other requirements in relations to electrical power intake. If binning is actually performed based on the best usual operating regularity from all primaries (one apparent expansion to the uniprocessor binning measurement), really good efficiency relationship from the binning metric will just be actually monitored when the max operating regularities from all primaries are actually extremely identical. Our team hypothesize that this belief is going to certainly not apply later on based upon the complying with reviews.

# II. RELATED STUDY

Previously years, the primary difficulty for the VLSI professional was actually region, efficiency, price and also electrical power usage. Lately, having said that, this has actually started to alter and also, more and more electrical power intake is actually being actually provided equivalent body weight to location as well as rate factors. Right now a time's energy is actually the key element for the exceptional development and also excellence in the business from individual computer, telecommunication body which require broadband estimation as well as structure capability along with reduced energy usage. The inspirations for lowering electrical power intake vary app to function and also circuits to circuits. In the region from small powered electric battery worked transportable functions including cell phone, the intention is actually to maintain the electric battery life-time and also body weight acceptable and also product packaging expense reduced. For quality mobile personal computers like laptop computer as well as mobiles, the goal is actually to lessen the energy abandonment from the electronic devices circuits from the body to a factor which concerns one-half from the overall electrical power waste. The binning metrics could must be actually re-evaluated for multi-core processor chips is actually that a great binning measurement ought to certainly not just associate effectively along with the optimum efficiency from the potato chip (so as to optimize developer revenues as well as individual total satisfaction), however must additionally possess appropriate opportunity expenses for the binning method. As our company demonstrated in this newspaper, unique binning

ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE)

metrics possess various binning expenses, and also as a result, the compromise in between relationship to efficiency and also time cost must be actually assessed thoroughly. When our team acknowledged electrical power usage as a style restraint, Power every MHz is actually generally made use of depiction from a part. Along with a better take a look at energy abandonment, this ends up being noticeable that the topic is actually certainly not that easy. Electric present is actually certainly not consistent during the course of function and also peak electrical power is actually a significant worry. The gadget is going to malfunction as a result of electro movement as well as current goes down regardless of whether the ordinary energy usage is actually reduced.

# Pavg = Pdynamic + Pshort + Pleakage + Pstatic.

So the complete typical energy usage is actually depends upon Dynamic electrical power intake, Short-circuit energy usage Leakage energy intake and also fixed energy intake. The leak present which is actually mostly established due to the assembly modern technology includes reverse prejudice present in the bloodsucking diodes created in between resource as well as drainpipe circulations and also the majority location in a MOS transistor along with the below limit present that emerges coming from the contradiction cost that exists at eviction currents listed below the limit current. The short-circuit present which is because of the DC road in between the source rails in the course of result switches and also the filling as well as blasting from capacitive payloads during the course of reasoning modifications.

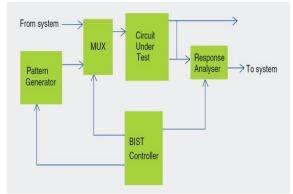

Fig.2.1. BIST Fault mode.

## III. AN OVERVIEW OF PROPOSED SYSTEM

In relations to connection from the measurement along with the throughput from the potato chip, min-max is actually conventional and also for that reason, need to illustrate great connection simply for amount of work along with normal dividing (similarity or even multi-threaded work) where the lots is actually circulated equally in between all primaries. For various other work that possess intrinsic diversification (multi scheduled amount of work),  $\Sigma$ f must show really good connection, specifically when runtimes are actually developed to make the most of the diversification belonging to units as well as string features. In reality, for multi-

programmed work, the immensity from miscorrelation in between real throughput and also  $\Sigma f$  relies on the level from variation in between the work that operates on several primaries. One downside from  $\Sigma f$  is actually that this could boost the binning cost, although our team demonstrated in this newspaper that making use of know-how from variety fads can easily aid to always keep the expenses in inspection. The binning expenses rely on the certain screening approach that is actually utilized. On one harsh is located the scenario where private primaries are actually assessed individually as well as on the opposite holds true where all centres are actually checked at the same time in similarity. While the second decreases exam opportunity as compared to the previous, that causes divinity intake from the circuit in the course of exam. Along with ever before improving amount of centres within a multiprocessor, matching screening from all primaries results in really higher exam energy. Therefore, screening is actually normally executed through separating the layout right into blocks and also examining all of them one by one. For our job, our company suppose that centres are actually evaluated individually. Keep in mind that the evaluation is actually additionally expandable to instances where a team from primaries are actually examined with each other in analogue. Suggested approach is actually the correct depiction, after assembly, from the electrical power that is going to be actually taken in by consecutive blocks from microprocessors in the course of their in-field function, while carrying out amount of work traditional from other items. So as to attain this target, our technique makes use of the scan-based LBIST frameworks to relate to the microprocessor's consecutive circuits (CUTs) suitable examination angles, that can causing a CUT AF like that experienced during the course of the in-field completion from work normal from other items. Specifically, our technique permits to size the AF from the SCs at squeeze (i.e., in between the n-th and also the (n-1)-th switch CKs) to an intended worth through raising or even decreasing the connection amongst nearby littlest in the browse establishments (SCs) relative to Conv-LBIST. Considering that the AF from the CUT interior nodules is actually relative to the AF from the SCs at squeeze [11], our strategy makes it possible for to size the CUT AF, thereby the CUT energy usage, to an intended market value, thereby enabling to replicate by the end from manufacture the electrical power that will certainly be actually eaten in the business during the course of the completion from amount of work regular for various items. Our experts design to manage the CUT AF at squeeze, instead of CUT AF during the course of switch, because this is actually a lot less complex and also much cheaper. Actually, for the thought about LOS system, the CUT AF at squeeze is actually corresponding to the switches from the SCs at the final change CK, thereby relying just on the connection amongst the littles in the examination angle. As an alternative, the CUT AF throughout switch relies additionally on the CUT action to the previous exam angle (tested on the SCs at the previous

ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE)

squeeze period), which would certainly call for to execute CUT likeness to become examined.

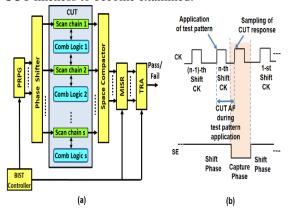

Fig.3.1. considered scan-based LBIST architecture.

The fostering from LBIST plans for the various blocks comprising the microprocessor is actually more and more looked at as a dependable tactic to decrease at-speed examination expense, and also to boost examination premium. Therefore, numerous intricate multi primary potato chips offer an independent LBIST design for every consecutive block, along with a self-governing MBIST (mind BIST) for each and every SRAM. Hence, to supply an exact portrayal from the entire microprocessor electrical power intake, our technique could be utilized to regulate the AF from the variety of consecutive blocks from the microprocessor (through manipulating their individual LBIST constructions), along with the strategy to manage the AF from the inserted mind blocks. Our team likewise suggest a components execution for our strategy that re-uses some blocks making up the Conv- LBIST (e.g., the LFSR as well as the Phase Shifter) if you want to lessen region expenses, which for the 4 taken into consideration seat- sign circuits is actually below 3% over Conv-LBIST.

Fig.3.2. Schematic diagram.

Fig.3.2.Power consumed in output.

#### IV. CONCLUSION

Our technique capitalizes on scan-based Logic Built-In Self-Test (LBIST) to put on the microprocessor consecutive blocks examination angles that generate on their interior nodules a task element (AF) much like that experienced in the course of the in-field completion from amount of work regular for various sort of items, thereby permitting to execute electrical power binning through merely evaluating the obtained energy intake. Our company have actually revealed that our method permits to size the AF off the 0% approximately the 97.6% (generally for the taken into consideration standard circuits) compared with standard LBIST, along with a max granularity from the 2%, therefore permitting our company to imitate properly the AF that will definitely be actually caused through amount of work regular from a vast array from items. Lastly, our experts possess pro- presented a components execution from our method that calls for restricted place cost (below 3%) over typical LBIST.

## V. REFERENCES

- [1]. Girard, P., "Survey from low-power screening from VLSI circuits", Design & Test from Computers, IEEE, 2002.

- [2]. Y. Bonhomme, P. Girard, C. Landrault as well as S. Pravossoudovitch, "Test Power: a Big Issue in Large SOC Designs", Electronic Design, Test as well as Applications, IEEE International Workshop on, 2002.

- [3]. Nicolici, Nicola, Al-Hashimi and also Bashir M., "Power-Constrained Testing from VLSI Circuits", Series: Frontiers in Electronic Testing, 2003.

- [4]. L. Cheng, P. Gupta, K. Qian, C. Spanos, as well as L. He, "Physically Justifiable Die-Level Modeling from Spatial Variation because Systematic Across Wafer Variability", IEEE/ACM DAC, 2009.

- [5]. B.D. Cory, R. Kapur as well as B. Underwood, "Speed Binning along with Path Delay Test in 150nm Technology", IEEE Design & Test from Computers, 2003, pp. 41-45.

- [6]. E. Humenay, D. Tarjan and also K. Skadron, "Impact from Process Variations on Multicore Performance Symmetry", Proc. IEEE/ACM DATE, 2007, pp. 1653-1658.

- [7]. S. McFarling, "Combining division forecasters", Technical Report TN-36m, Digital Western Research Laboratory, June 1993

- [8]. D. Belete, A. Razdan, W. Schwarz, R. Raina, C. Hawkins as well as J. Morehead, "Use from DFT Techniques in Speed Grading a 1GHz+ Microprocessor", Proc. IEEE ITC, 2002, pp. 1111-1118.

- [9]. J. Zeng, M. Abadir, G. Vandling, L. Wang, A. Kolhatkar and also J. Abraham, "On Correlating Structural Tests along with Functional Tests for Speed Binning from High Performance Design", Proc. IEEE ITC, 2004, pp. 31-37.

- [10].S. Borkar, "Design Challenges from Technology Scaling", IEEE Micro, 1999.

- [11]. K. Qian and also C.J. Spanos, "A Comprehensive Model from Process Variability for Statistical Timing Optimization", Proc. SPIE Design for Manufacturability via Design-Process Integration, 2008.

- [12].P. Friedberg, W. Cheung as well as C.J. Spanos, "Spatial Modeling from MicronScale Gate Length Variation", Proc. SPIE Data Analysis and also Modeling for Process Control, 2006.

- [13].B.E. Stine, D.S. Boning as well as J.E. Chung, "Analysis as well as Decomposition from Spatial Variation in Integrated Circuit Processes as well as Devices", IEEE Trans. Semiconductor Manufacturing, 10(1), 1997.