# A Passive 2<sup>nd</sup>-Order Sigma-Delta Modulator for Low-Power Analog-to-Digital Conversion

Angsuman Roy and R. Jacob Baker

Department of Electrical and Computer Engineering, University of Nevada, Las Vegas angsumanroy@gmail.com

Abstract—A passive 2<sup>nd</sup>-order sigma-delta modulator based on a cascade of first-order lowpass filters was designed, fabricated, and tested. A lumped RC filter is added in the loop of a conventional 1<sup>st</sup>-order passive sigma-delta modulator in order to improve the linearity of its transfer function. A low power edge-triggered comparator was designed and fabricated along with lumped components in ON Semiconductor's C5 500-nm process. The implementation achieved a THD below 1% for all frequencies between 10 Hz and 5 kHz. With a 5 V supply the power consumption of the sigma-delta modulator is 64.5 uW to 150 uW depending on the input signal.

### I. INTRODUCTION

There is a well-known trade-off between power consumption and speed/accuracy in the design of analog to digital converters (ADC). In applications such as remote sensing, often the power consumption is prioritized over accuracy. For a sigma-delta ( $\Sigma$ - $\Delta$ ) ADC a large portion of the power consumption comes from the use of an active integrator circuit. Thus, a logical place to look when trying to reduce the power consumption of a  $\Sigma$ - $\Delta$  ADC is to eliminate the active integrator. In this work we investigate performing the integration function using a simple passive filter. This is also the path taken by several other researchers [1] and [2]. However, in both [1] and [2] a conventional passive 1st- or 2ndorder loop filter is used [3]. An alternative  $2^{nd}$ -order passive  $\Sigma$ - $\Delta$  topology proposed in this paper offers low-power consumption while preserving sufficient accuracy. The topology may be implemented using switched-capacitor techniques which would result in near zero static power consumption. Investigating this approach can be the focus of future research activities.

### II. PASSIVE SIGMA-DELTA TOPOLOGIES

The conventional 1<sup>st</sup>-order  $\Sigma$ - $\Delta$  modulator is shown in Fig. 1 [3]. This topology uses a comparator, two resistors and a capacitor. When operating properly the average currents through each resistor are equal. The two resistors must match for the gain of the modulator to be unity. The capacitor performs the integration function. This topology has significant nonlinearity due to the voltage swing at the positive comparator input which is the voltage across the integrator (integrating capacitor) [3]. The output voltage is a function of the input voltage, quantization error voltage, and integration node voltage as shown in Eq. (1). The signal transfer function (STF), noise transfer function (NTF), and distortion term (DT) are given in Eqs. (2), (3), and (4)

respectively. Note that the signal undergoes lowpass filtering during the conversion while the noise is highpass filtered and then, ideally, removed with a digital filter. Unfortunately, the distortion term also shows a lowpass response which can corrupt the input signal and be impossible to remove. Note that when using an active integrator the distortion term isn't present in the output of the modulator because the voltage across C1 is held constant.

$$V_{out} = \frac{1}{1 + sR_1C_1}V_{in} + \frac{sR_1C_1}{1 + sR_1C_1}V_{Qe} + \frac{-2}{1 + sR_1C_1}V_{int}$$

$$STF = \frac{1}{1 + sR_1C_1}$$

(1)

$$NTF = \frac{sR_1C_1}{1 + sR_1C_1} \tag{2}$$

$$1 + sR_1C_1$$

$$-2$$

(3)

$$DT = \frac{-2}{1 + sR_1C_1} \tag{4}$$

R1 C1 VCM Calk Vout

**Figure 1** – Conventional 1<sup>st</sup>-order  $\Sigma$ - $\Delta$  modulator.

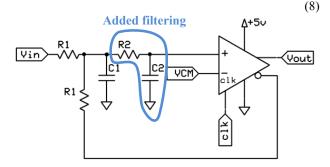

The modified  $2^{nd}$ -order  $\Sigma$ - $\Delta$  modulator proposed in this paper is shown in Fig. 2. This topology takes the conventional  $1^{st}$ -order  $\Sigma\Delta$  modulator and adds an RC filter between the feedback summing node and the positive input of the comparator. The motivation for the addition of the RC filter is to try to reduce the voltage swing at the positive node of the comparator. Equation (5) shows the output voltage as a function of the input voltage, quantization error voltage and integration node voltage. The signal transfer function, noise

transfer function and distortion term for the proposed topology are shown in (6), (7), and (8) respectively. It can be seen from the NTF that the noise shaping is indeed 2<sup>nd</sup>-order.

$$V_{out} = \frac{1 + sR_2C_2}{1 + sR_2C_2 + sR_1C_1} \cdot V_{in} + \frac{s(sR_1C_1R_2C_2 + R_1C_1)}{1 + sR_1C_1 + s^2R_1C_1R_2C_2} \cdot V_{Qe} + \frac{1}{1 + sR_1C_1 + (1 + sR_2C_2)} \cdot V_{int}$$

(5)

$$STF = \frac{1 + sR_2C_2}{1 + sR_2C_2 + sR_1C_1}$$

$$NTF = \frac{s(sR_1C_1R_2C_2 + R_1C_1)}{1 + sR_1C_1 + s^2R_1C_1R_2C_2}$$

(6)

$$DTF = \frac{1}{1 + sR_1C_1 + (1 + sR_2C_2)}$$

(7)

**Figure 2** – Proposed  $2^{nd}$ -order  $\Sigma$ - $\Delta$  modulator.

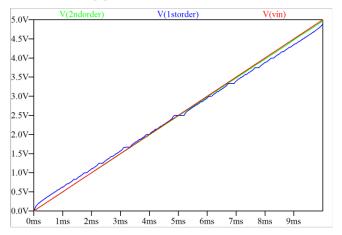

To compare the different topologies, a simulation was performed using an ideal comparator to remove the effects of any component nonlinearities and focus on just the effect of the added RC filter. For the  $1^{\text{st}}$ -order modulator, the values of R1 and C1 were set to  $1~\text{M}\Omega$  and 10~pF respectively. For the  $2^{\text{nd}}$ -order modulator the values of R1, R2, C1, and C2 were set to  $50~\text{k}\Omega$ ,  $1~\text{M}\Omega$ , 10~pF, and 10~pF respectively. A 0 to 5V 10 ms ramp (red trace) applied to the input with the filtered outputs of the  $1^{\text{st}}$ - (blue trace) and  $2^{\text{nd}}$ -order (green trace) modulator are shown in Fig. 3. Clearly, the performance of the modified  $2^{\text{nd}}$ -order modulator is improved over the conventional  $1^{\text{st}}$ -order topology.

### III. INTEGRATED CIRCUIT IMPLEMENTATION

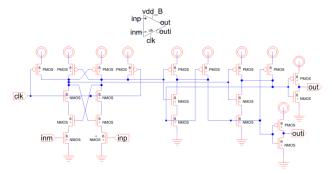

To investigate the real world performance of this novel topology, an integrated circuit implementation was designed, fabricated and tested. The heart of the  $\Sigma$ - $\Delta$  modulator is the clocked comparator. The clocked comparator was designed for minimal power consumption. The schematic of the comparator is shown in Fig. 4. The comparator is composed of a cross coupled latch connected to an S-R latch which causes the

output to only change on the rising edge of the clock. In order to reduce contention current the input devices are long L NMOS. Additional details covering the design considerations can be found in [4].

**Figure 3** – Linearity comparison between 1<sup>st</sup>- and 2<sup>nd</sup>-order modulators.

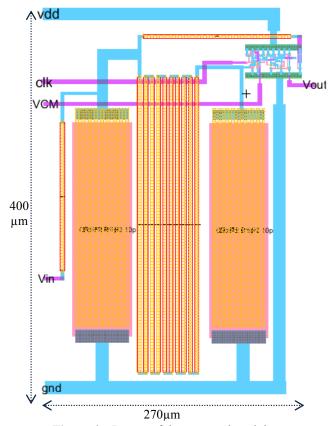

On-chip passive lumped components are added to the comparator in order to implement the  $\Sigma$ - $\Delta$  modulator of Fig. 2 in integrated circuit form. The values for R1, R2, C1 and C2 are (nominally) 50 k $\Omega$ , 1 M $\Omega$ , 10 pF and 10 pF respectively. The resistors were fabricated using the high-resistance poly2 layer in the C5 process. The capacitors are formed using plates of poly1 and poly2 layers (poly-poly caps).

Figure 4 – Schematic of the low-power comparator.

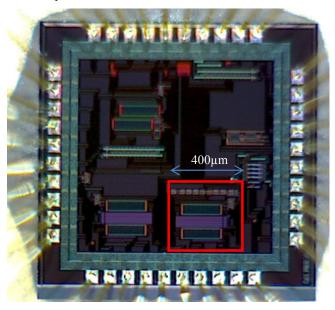

A microphotograph of the chip is shown in Fig. 5. The proposed modulator can be seen in the lower right-hand corner of the chip in the red square and the corresponding layout, measuring 270  $\mu$ m by 400  $\mu$ m, is seen in Fig. 6.

## IV. INTEGRATED CIRCUIT TEST RESULTS

The integrated circuit was tested in order to quantify its DC performance, AC performance, and power consumption. A 2<sup>nd</sup>-order 16 kHz low-pass filter with a Q of 0.33 was added to the output of the modulator in order to convert the one-bit data stream back into analog. The supply voltage was 5 V and the common-mode voltage was set to 2.5 V. A 5 V, 10 MHz square wave was used as the clock signal. DC linearity was tested by comparing input and output voltages using a 6.5

digit multi-meter. AC testing was done using a low distortion oscillator and looking at the total harmonic distortion (THD) at the output.

**Figure 5** – Chip microphotograph. The proposed modulator is surrounded by the red box.

**Figure 6** – Layout of the proposed modulator.

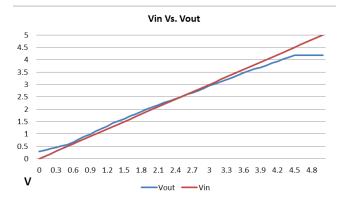

The measured DC transfer curves are seen in Fig. 7. There is an offset of a few hundred mV near ground and a considerably larger offset near VDD (+ 5 V). This is to be expected in a  $\Sigma$ - $\Delta$  modulator using ground and VDD for the fed back reference voltages. The filtered output voltage of the  $\Sigma$ - $\Delta$  modulator is limited to 4.2 V which is due to limitations of the comparator working with large input signals. There is also a small amount of gain error. While gain error is undesirable it is not as important as nonlinearity in the performance of an ADC.

Figure 7 – Input and output DC transfer curve.

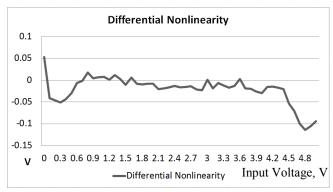

While DC plots are usually not given for  $\Sigma$ - $\Delta$  ADCs here we have added significant filtering in order to make the output (nearly) static. This result is shown in Fig. 8 where the x-axis is the  $\Sigma$ - $\Delta$  ADC's input voltage. The y-axis indicates the difference between the ideal output and the measured output in Volts. The differential nonlinearity (DNL) plot for the topology shows that DNL is kept to within 0.4 % when the input voltage is bounded between 0.4 V and 4.2 V. Note that here we use percentages because the "effective" least significant bit (LSB) is determined by the amount and type of digital filtering used on the output of the modulator. Since the slope of the line is relatively linear, the corresponding AC performance of the  $\Sigma$ - $\Delta$  modulator should be quite good. Note, as mentioned earlier, that here we are trading off accuracy for power consumption, discussed in more detail shortly.

**Figure 8** – Using filtering added to the output of the modulator in order to make it stable for determining DNL.

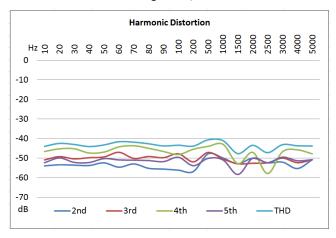

The measured harmonic distortion of the  $\Sigma$ - $\Delta$  modulator is shown in Fig 9. The input signal is a 1.5 V sine wave with a 2.5V DC offset. The total harmonic distortion (THD) remains under 40 dB below the fundamental for all frequencies between 10 Hz and 5 kHz. The dominant contributor to the THD is the 4<sup>th</sup> harmonic. Interestingly, the 2<sup>nd</sup> harmonic is the smallest component of the THD. Note that this data was harvested using a digital oscilloscope with an 8-bit vertical front-end (< 50 dB SNR which is comparable to performance of the modulator that is being tested).

**Figure 9** – Measured total harmonic distortion of the modulator.

Power consumption of the  $\Sigma\text{-}\Delta$  modulator is quite low despite a 5 V supply voltage. Using a 10 MHz clock the measured supply current is only 12.9  $\mu A$  when the output of the  $\Sigma\text{-}\Delta$  modulator is at the extreme ends of its transfer function. For the worst case of when the  $\Sigma\text{-}\Delta$  modulator is switching between high and low for an equal amount of time the measured supply current is 30  $\mu A$ . This is the case in the middle region of the  $\Sigma\text{-}\Delta$  modulator's transfer function. These values correspond to average power consumption between 64.5  $\mu W$  and 150  $\mu W$ . Using a modern process with a  $\sim 1$  V supply voltage and dimensions well under 500 nm the power consumption of the topology may reach nW levels making this topology very useful in sensors powered by energy harvested from mechanical vibrations and/or solar cells.

Note that in this work power is continuously dissipated by the resistors used in the modulator. Since these resistors are large this power is fairly small and it may be possible to further reduce the power and the layout area (significantly) by replacing the resistors with switched-capacitors (SC). The drawback of this approach is the need for a clock generation circuit to provide non-overlapping clocks to the SC resistors. The benefit is essentially zero power dissipation at all times except for when the clock is transitioning high or low. The other test structures seen on the chip in Fig. 5, outside the red box, will be used to investigate this possibility in future work.

The performance of the proposed  $\Sigma$ - $\Delta$  modulator is compared to two other designs in Table 1. Although performance is worse than the other two designs, it is important to keep in mind that the proposed modulator is implemented in a 500-nm process with a 5 V supply. Also the results for the proposed  $\Sigma$ - $\Delta$  modulator are measured and not simulated.

| Parameter            | 2 <sup>nd</sup> Order ∑-<br>Δ Modulator<br>in This Work<br>(Measured) | 2 <sup>nd</sup> Order ∑-<br>Δ Modulator<br>in [5]<br>(Simulated) | 2 <sup>nd</sup> Order ∑-<br>Δ Modulator<br>in [2]<br>(Simulated) |

|----------------------|-----------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|

| Process              | 500 nm                                                                | 350 nm                                                           | 350 nm                                                           |

| Resolution<br>(ENOB) | 8-bit                                                                 | 12-bit                                                           | 10-bit                                                           |

| Power<br>Consumption | 100µW<br>(typical)                                                    | 120 μW                                                           | 50 μW                                                            |

| Signal<br>Bandwidth  | 5 kHz                                                                 | 1 kHz                                                            | 4 kHz                                                            |

**Table 1** – Comparing performance of the proposed  $\Sigma$ - $\Delta$  modulator to [2] and [5].

### V. CONCLUSION

The low power  $\Sigma$ - $\Delta$  modulator proposed in this paper retains relatively good precision despite the elimination of the active-integrator to reduce power dissipation. Although the linearity isn't as good as a  $\Sigma$ - $\Delta$  modulator implemented using an active integrator, the presented circuit should find use in applications which heavily prioritize power consumption and don't require high precision. Although the  $\Sigma$ - $\Delta$  modulator was implemented in a 500-nm CMOS process the concepts presented should scale to smaller, lower-power, processes.

# REFERENCES

- [1] De Melo, Joao L. A. "A Low Power 1-MHz Continuous-Time ΣΔM Using a Passive Loop Filter Designed With a Genetic Algorithm Tool," *ISCAS 2013*. (2013): 586-589.

- [2] Guessab, S., P. Benabes, and R. Kielbasa. "Passive Delta-Sigma Modulator for Low-Power Applications," MWSCAS '04. (2004): 295-298.

- [3] Baker, R. Jacob, CMOS Mixed-Signal Circuit Design, Second Edition, John Wiley and Sons, Inc., 2009.

- [4] Baker, R. Jacob, CMOS Circuit Design, Layout, and Simulation, Third Edition, John Wiley and Sons, Inc., 2010, pp. 452-455.

- [5] Gundel, Adnan, and Carr, William N. "A Micro Power Sigma-Delta A/D Converter in 0.35μm CMOS for Low Frequency Applications," *LISAT 2007*. (2007): 1-7.