# An Improved Low-Voltage Low Power Fully-Differential Double Folded Cascode Class AB Opamp for Pipeline ADC Applications

Pennapati Nagamallaiah<sup>1</sup>, S.Varalakshmi<sup>,2</sup>, G.Krishna Murthy<sup>3</sup>

<sup>1</sup>Assistant Professor(Adhoc) Department of ECE, JNTUACEP, Pulivendula, A.P, India.

<sup>2</sup> Assistant Professor(Adhoc) Department of ECE, JNTUACEP, Pulivendula, A.P, India.

<sup>3</sup>Assistant Professor(Adhoc) Department of ECE, JNTUACEP, Pulivendula, A.P, India.

(nagamallaiah8787@gmail.com, varalakshmi1190@gmail.com, krishna.goggi24@gmail.com)

Abstract—This paper presents with a fully differential amplifier(FDA) consists high output voltage swing, less susceptibility to common mode noise, and cancellation of even-order nonlinearities of double folded cascode and class AB output with continuous time common mode feedback (CMFB) network ,this function is control the common mode voltage. High-Gain loop consumes less than 1.2mW at 1.8Volts single supply voltage in a 0.18µm CMOS process in Cadence Spectre Circuit Simulator. This circuit design of the CMFB circuit is more challenging than the actual op-amp design due to the difficulty of properly compensating it. However, it is challenging to integrate high-speed, highresolution ADCs in low cost IC processes, when compared to conventional designs, enabling operation at higher clock frequencies as the class AB stage causes the slew limiting in the first stage and power dissipation is decreasing.

*Keywords*— Analog-to-digital converter (ADC); fully differential operational amplifier; common mode feedback (CMFB); class AB; double folded cascode(DFC).

# I. INTRODUCTION

Designing analog-to-digital converters (ADCs) with high bit resolution, low power, low noise ratio and high sampling rate(speed) have five key challenges to be considered. Pipe line ADCs are commonly used for power efficient high speed conversion wide bandwidth input signals and has good accuracy. It offers an attractive combination of speed, resolution, low power consumption and small die size. The speed, a c c u r a c y a n d resolution of pipeline ADC is greater than to flash ADC. It can be implemented in wireless communication systems and can be determined by settling behavior of operational amplifiers, as opamps are integral parts and basic building blocks used in most analog circuits [1]. Settling speed depends on not only a single pole settling, which is the virtual ground and output will settle exponentially with time constant, but also on unity-gain frequency. As System on Chip (SoC) technologies are remarkably increasing, high-performance opamps are used in ADCs significantly. A gain boosted folded

cascode architecture is used in the design of amplifier, which is used in the proposed an ADC. Higher speed is required for future application such as wireless communication. ADCs can limit the performance characteristics of wireless devices as they are power demanding blocks, especially in receiver systems to fulfill the required settling-time with minimum current consumption.

An ADCs encapsulates three key performance metrics: speed, accuracy, and power, as well as their associated tradeoffs with respect to the associated technology. Therefore, decreasing the total power dissipation could yield significant power saving. The system is fully differential amplifier to improve accuracy, power supply rejection ratio and minimize the even harmonic distortion are three important advantages that have. In order to obtain higher DC gain, analog designers tend to design multi-stage topologies and these techniques depend on using cascode structures. In other words, keeping a high DC gain, which leads to use multi-stage amplifiers, is done by applying cascode technique. An improved cascode circuit that combines both high gain and high speed is developed. The folded cascode architecture or the mirrored cascode architecture is designed to increase the input and output voltage swings [2]. In order to increase the open-loop gain, cascode techniques are often applied in opamp design. Recently, in low power voltage, class AB output stage is used increasingly when high efficiency is becoming significant in analog designs, and it has high output impedance.

In our designs, a fully differential folded cascode topology is implemented and the gain enhancement is obtained by replacing the regular cascode circuits with active cascode circuits.Our proposed design is based on a fully differential opamp includes a DFC and class AB output stage with continuous time common mode feedback network which is appropriate for driving 12-bit pipeline ADC with foreground calibration. The speed of a pipelined ADC is always limited by the opamp settling time in the S/H "hold" phase. To optimize the speed, need to maximize the loop transmission bandwidth. The conceptual difference between double and single processing is that, it requires extra feedback to control the output common-mode component in fully differential amplifiers. an operational amplifier in an ADC must be able to drive large output swing in one clock period. For small signals, the settling time of an operational amplifier is mainly dependent on the bandwidth of the amplifier. On the other hand, for large signals, the slew rate of the amplifier becomes a major contributor to the settling time. Therefore, both high slew rate and wide bandwidth are important factors in choosing the right architecture for the amplifier in an ADC. This design provides a much smaller load capacitance to the output of the amplifier that leads higher speed and larger slew rate. An DFC operational-amplifier topology that achieves improved DC gain and common-mode rejection without sacrificing slew rate.

The organization of this paper is as follows: Section II describes existed and the proposed FDAs, Section III reports the simulation results which are achieved in 0.18 $\mu$ m CMOS technology and also comparison with previous works given. Section IV explains tradeoff in speed, accuracy and area. Section V explains pipe line ADCs applications and advantages. The appropriate analysis for testing opamp is explained with suitable opamp application and at last conclusions are drawn in Section VI respectively.

#### II. FDA DESCRIPTION

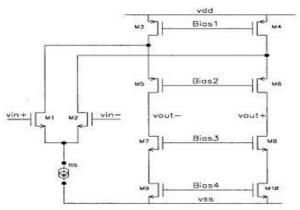

An operational amplifier is one of the most important blocks in the design of a pipelined ADC. In this design, a gainboosted fully differential folded-cascode amplifer is implemented. Based on the gain-boost principle, we are able to boost the DC-gain and achieve a satisfactory settling behavior as well. A fully differential amplifier (FDA) has a wide range of usage because of its innate immunity to common mode signals and clock feed through. It is a DC-coupled high gain folded-cascode opamp is to apply cascode transistors to the input differential pair but using transistors opposite in type from those used in the input stage. The differential-pair transistors M1 and M2 are n-channel transistors whereas the cascode transistors M5 and M6 are pchannel transistors.

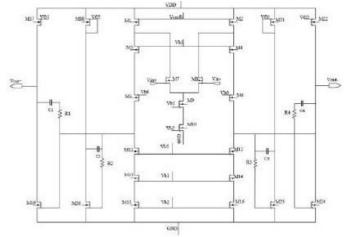

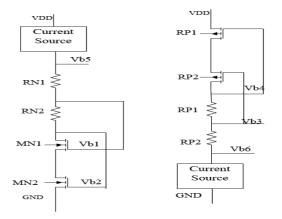

This arrangement of opposite-type transistors allows the output of the amplifier to be taken at the same bias-voltage level as the input signals shown in figure 1., i.e. the output common-mode voltage can be set at the same level as the input common mode voltage, which is convenient for pipelined architecture since the output signal of one stage would be the input for the next stage[3]. FDA is used to convert an analog signal to digital signal and is suitable for driving highprecision ADCs that mostly have differential inputs. Generally CMFB circuits are of two types: Switched Capacitor CMFB circuit and Continuous time CMFB circuit. It has common mode input and differential output[4]. It is needed to stabilize the differential output voltage at a common level. The common mode feed-back (CMFB) is generally needed for two major reasons. Figure 2 shows one is to control the common mode voltages at different nodes that negative differential feedback can stabilize. The other one is to overwhelm the common mode components that tend to saturate with the diversity of stages. Figure 3. shows a general block diagram of a fully differential amplifier with a CMFB.

Figure 2 :CMFB

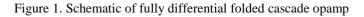

A CMFB circuit has a common mode signal detector and a sense amplifier. Common mode output voltage is the average of the differential outputs. Figure 3 shows a fully differential double folded cascode class AB opamp with continuous time common mode feed-back network (CMFN). Figure 4 shows CMFN is not only a simple element but also it has high common mode rejection ratio (CMRR) which is significantly important in opamp performance, so flowing current must be adjusted carefully.

Generally, to stabilize the common mode voltages for fully differential analog systems in order to adjust common mode currents a CMFN is required. Any increment in bias current is fulfilled by increasing the width of transistors in current source design and this is also valid for composite transistors. If without CMFN, the transistors in system may easily drift away from saturation region due to mismatch and other process tolerances and cause a system malfunction for especially for low voltage applications. In order improve the performance of CMFB, several circuits are proposed, which are resistor averaging circuit, switched capacitor averaging circuit and differential difference amplifier circuits. In this paper presented shown in figure 4. is CMFN circuit for low voltage, large output swing and high speed applications.

Unlike the conventional folded-cascode amplifier, to achieve high slew rate at the output, both PMOS sourcing and NMOS sinking current sources are dynamically controlled with their respective diode-connected transistors. This helps in achieving accurate current sensing. The current sense circuit presented here offers an inherent 180 °phase shift between the class-AB output current and the respective sense currents through current mirrors. Since the current sensing circuit is formed by current mirrors with high quiescent currents, the sensing is fast.

Figure 3. A fully differential double folded cascode class AB

| In such a scenario the linear amplifier's power consumption |

|-------------------------------------------------------------|

| can be reduced by decreasing the bias current such that a   |

| minimum required UGF is achieved[5].                        |

| Name of<br>Transistor | Length<br>(µM) | Width<br>(µM) | Name of<br>Transistor      | Length<br>(µM) | Width<br>(µM) |

|-----------------------|----------------|---------------|----------------------------|----------------|---------------|

| M1,M2                 | 1              | 8             | M17,M18                    | 0.5            | 3             |

| M3,M4                 | 0.5            | 3             | M19,M20                    | 0.5            | 1             |

| M5,M6                 | 0.18           | 1             | M21,M22                    | 0.5            | 3             |

| M7,M8                 | 0.18           | 10            | M23,M24                    | 0.5            | 1             |

| M9,M10                | 1              | 2             | M25,M26,M27<br>M28,M29,M30 | 1              | 8             |

| M11,M12               | 0.18           | 0.5           | M31,M32<br>M33,M34         | 0.28           | 11            |

| M13,M14               | 0.5            | 1             | M35                        | 1              | 2             |

| M15,M16               | 1              | 2             | M36                        | 1              | 2             |

TABLE I .TRANSISTOR SIZES OF PROPOSED OPAMP

Figure  $4:\mbox{A fully differential double folded cascode class AB with CMFN.}$

# ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE)

Significant area savings and a higher cutoff frequency are two main specifications of this design. As it can be observed from Fig. 3, common gate transistors are for increasing gain and to reduce the differential input capacitance.

|  | TABLE II.Design | specifications | of op-amp | and ADC |

|--|-----------------|----------------|-----------|---------|

|--|-----------------|----------------|-----------|---------|

| Specification                            | Value   | units |

|------------------------------------------|---------|-------|

| Power supply, VDD                        | 1.8     | Volts |

| Capacitor,CL                             | 2       | pF    |

| Resistors R1=R4                          | 200     | Ω     |

| Resistors R <sub>2</sub> =R <sub>3</sub> | 100     |       |

| I <sub>Tail</sub>                        | 160     | μΑ    |

| Capacitors                               | 6       | pF    |

| V <sub>CM</sub>                          | 900     | mV    |

| Gain                                     | 117     | dB    |

| Phase Margin                             | 65      | Deg   |

| CMRR                                     | 72      | dB    |

| Power consumption,<br>P <sub>C</sub>     | 1.2     | mW    |

| High Speed                               | 100-300 | MS/s  |

| high resolution                          | 10-16   | Bits  |

| CMRR                                     | >70     | dB    |

| PSRR                                     | >70     | dB    |

| Dc gain of common<br>mode path           | 82      | dB    |

| Phase margin of fully differential       | 82      | Deg   |

| Slew rate                                | 12.5    | V/    |

| Technology                               | 0.18    | μm    |

The minimum size of the capacitors is determined in order to limit the SNR and for the maximum signal swing limited by the power supply.In Table II given design specification of proposed op-amp and pipe line ADCs.

Figure 5. shows the suitable high swing bias network for the proposed opamp. In order to minimize the systematic mismatch error and to scale the circuit with this chosen values.

| TABLE III.Re | presentation ( | of Chosen | parameters |

|--------------|----------------|-----------|------------|

|--------------|----------------|-----------|------------|

| Chosen Parameters                       |        | Values | units |

|-----------------------------------------|--------|--------|-------|

| Resistors RP1=RP2                       |        | 40     | kΩΫ   |

| NMOS<br>transistors<br>PMOS transistors | Length | 1      | μΜ    |

|                                         | Width  | 2      | μМ    |

|                                         | Length | 1      | μΜ    |

| Width                                   |        | 8      | μΜ    |

| Current source                          |        | 10     | μΑ    |

Figure 5 . Biasing circuit of proposed opamp.

## III. SIMULATION RESULTS

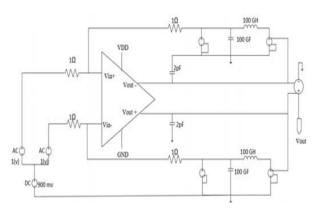

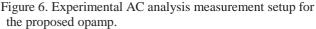

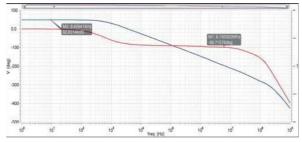

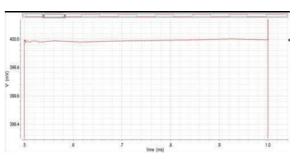

Fig. 6 shows the qualified setup for doing AC analysis for fully differential and common mode path that gain and phase margin can be obtained. Fig. 7 shows the gain and phase margin of designed opamp which are 117 dB and 65-degree, respectively. Also, Fig. 8 shows the gain of 82 dB and phase margin of 82-degree for common mode path. The transient analysis has been done to Vo+, Vo-, Vdiff, and Vocom. Fig. 9 shows transient analysis which illustrates that the settling time

Figure 7. Gain and phase of proposed opamp.

Figure 8. Gain and phase of common mode path.

Figure 9. Transient analysis of opamp.

is well enough for driving proposed ADC. In this design, the power consumption is 1.2 mW. The simulation results are given in Table I, and in order to verify the performance of proposed design, comparison with other previous works has been done in Table V which proves it is well suited for ADC applications as it has high gain, high speed, and low power dissipation.

## IV. COMPARATIVE DESCRIPTION OF ADCS WITH PROPOSED PIPELINE ADC

Different ADC architectures can be used depending on the required accuracy, speed and power consumption. So there is a tradeoff in speed, accuracy and area. Also it consumes more power.

| Architecture                | Latency | Speed           | Accuracy        | Area   |

|-----------------------------|---------|-----------------|-----------------|--------|

| Flash                       | No      | High            | Low             | High   |

| SAR                         | No      | Low-<br>Medium  | Medium-<br>High | Low    |

| Folding +<br>Interpolating  | No      | Medium-<br>High | Medium          | High   |

| Delta-Sigma                 | Yes     | Low             | High            | Medium |

| Pipeline                    | Yes     | Medium-<br>High | Medium-<br>High | Medium |

| Proposed<br>pipeline<br>ADC | Yes     | High            | High            | Low    |

Table IV : Comparison of different ADCs

Comparison of different ADCs

In the table, even though the supply voltage and power dissipation in previous works nominated in references 4 to 6 are better than the proposed opamp, their DC gains are

low. Even when considering the work in reference 7, it can be observed that supply voltage and phase margin is better than the proposed opamp, but slew rate is not too appropriate and DC gain is low with respect to our design. Many high performance ADCs are now being designed with differential inputs. A fully differential ADC design offers the advantages of good common-mode rejection, reduction in second-order distortion products, and simplified dc trim algorithms [6]. Although they can be driven single-ended, a fully differential driver usually optimizes overall performance.

Pipelined ADC is a Nyquist –rate analog to digital converter [3]. It is a good choice among other analog to digital converter architectures for sampling rate from few mega samples per second to higher sampling rates. Resolution for such converters ranges from 8 to 16 bits [7]. Pipelined ADC is one of the most efficient ADC used in today's consumer electronics.

TABLE V.COMPARISON OUTCOMES WITH OTHER OPAMPS

| Parameters           | Proposed | [2]  | [5]  | Unit  |

|----------------------|----------|------|------|-------|

| Supply<br>Voltage    | 1.8      | 1.2  | 0.8  | V     |

| Power<br>Dissipation | 1200     | 36   | 1    | μW    |

| Slew Rate            | 12.5     | 20   | 0.12 | (V/µs |

| DC Gain              | 117      | 33.8 | 51   | dB    |

| Phase<br>Margin      | 65       | 45   | 65   | deg   |

## V. PIPE LINE ADC APPLICATIONS AND ADAVANTAGES

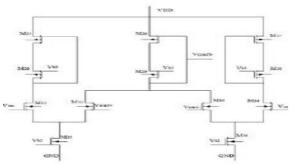

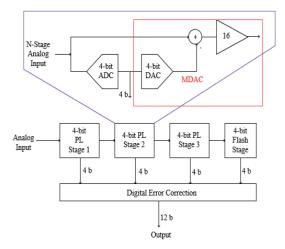

Opamps are used as drivers for enhancing the gain and level shifting ,to match the input range of the ADC. The task of selecting appropriate opamp is not straightforward and opamp performance must be measured under identical conditions in ADC applications. Some important specifications are fast settling to ADC transient, high bandwidth, low noise, low distortion, low power, etc. Fig. 7 shows the appropriate 12-bit pipeline ADC with foreground calibration. It is a 12-bit pipeline ADC using three 4-bit stages and one 4-bit flash ADC. In other words, each stage of a pipeline ADC resolves 4 bits and it has a digital error correction logic. Each of the identical stages contains a sub-ADC and MDAC[8]. Calibration parts consist of three 4-bit adders and also three D-Flip flops. Pipeline architecture is appropriate and suitable application for this proposed opamp due to balanced power, speed, and accuracy. Pipelined ADCs are used in a variety of applications such as: mobile systems, CCD imaging, ultrasonic medical imaging, digital receivers, base stations, digital video (e.g. HDTV), Xdsl, cable modems, and fast Ethernet This output result can suffer from errors and the digital data outcome may not

## ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE)

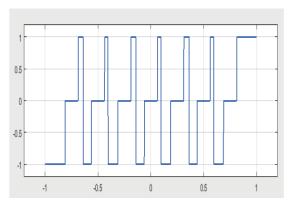

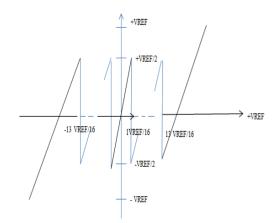

represent the real and correct values because of the presence of offset voltages in the comparators of 4-bit flash ADC is shown in Figure 10. Residue transfer curve for a 4 bits/stage is shown in Figure 11 and Figure 12 shows the output of 12-bit pipeline ADC.

Figure 10. 12-bit pipeline ADC.

Figure 11. Residue transfer curve for a 4 bits/stage.

Figure 12. Output of 12-bit pipeline ADC.

Table VI: Pipeline ADC Specifications

|                      |       | •     |  |

|----------------------|-------|-------|--|

| Specification        | Value | Units |  |

| Resolution           | 12    | bits  |  |

| Sample Rate          | 200   | MHz   |  |

| Power Supply         | 1.8   | V     |  |

| Vcm (Op-amp)         | 900   | mV    |  |

| Power<br>Consumption | 1.2   | mW    |  |

| Tail Current         | 160   | μΑ    |  |

| Power Supply         | 1.8   | V     |  |

#### VI. CONCLUSION

System design and transistor level design has been done using Cadence Spectre circuit simulator because it provides fast, high precision simulations for mixed-signal circuits and waveforms have been viewed using waveform viewer. In order to define the performance of an ADC, performance parameters play a very vital role and it is really important to ensure that the ADC is working well by measuring its static and dynamic parameters. A fully differential double folded cascode class AB operational amplifier with continuous time common mode feedback network is designed and simulated using cadence simulator in 0.18 µm CMOS process [9]. In order to check and verify the well-performance of the design, different tests have been done and shown good agreement. In Analog-to-Digital converters, high resolution and high speed are two important specifications which our design tries to achieve these where the proposed opamp can be employed as an efficient pipeline ADC driver. The best thing about a pipeline ADC is that it can provide high throughput rates and occupy small die area.

#### REFERENCES

- M. Ahmed, F. Tang, and A. Bermak, "A 14-bit 70MS/s pipeline ADC with power-efficient back-end stages," 2015 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Singapore, 2015, pp. 154-157.

- [2] A. Atac, A. Geller, R. Wunderlich, and S. Heinen, "A low power high GBW Fully Differential sub threshold CMOS opamp for CT sigma-Delta modulators," 2011 7th Conference on Ph.D. Research in Microelectronics and Electronics, Trento, 2011, pp. 205-208.

- [3] P.Wu, R.Schaumann, P.Latham, "Design onsiderations For Common-Mode Feedback Circuits in Fully-Differential Operational Transconductance Amplifiers with Tuning," IEEE International Symposium on Circuits and Systems, vol.3, June 1991, pp. 1363 –1366.

- [4] Franco Maloberti, "Data Converters," Springer, 2007.

- [5] M. R. Valero, S. Celma, N. Medrano, B. Calvo, and C. Azcona, "An ultra low-power low-voltage class AB CMOS fully differential OpAmp," 2012 IEEE International Symposium on Circuits and Systems, Seoul, 2012, pp. 1967-1970.

- [6] S. Zhang, Z. Zhu, H. Zhang, Z. Xiong, and Q. Li, "A 90-dB DC gain high-speed nested gain-boosted folded-cascode opamp," 2015 11th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Glasgow, 2015, pp. 357-360.

#### ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE)

- [7] R. Zou, "Design of a Fully Differential GAIN Boosted Operational Amplifier for High Performance ADC," 2013 Sixth International Conference on Business Intelligence and Financial Engineering, Hangzhou, 2013, pp. 539-541.

- [8] Designing of a MDAC Stage for 10-bit 100 MSPS Pipeline ADC James, Jaison (2016) Designing of a MDAC Stage for 10-bit 100 MSPS Pipeline ADC. eprints NITR.3.

- [9] O.Choksi and L.R.Carley, "Analysis of Switched-Capacitor Common-Mode Feedback Circuit," IEEE Transactions on circuits and systems –ii: analog and digital signal processing, vol.50, no. 12, december 2003, pp. 906-917.

*I*, Pennapati Nagamallaiah, working as Professor (Adhoc) in ECE, in JNTUACEP, Pulivendula, A.P, India. Iam pursuing my Ph.D in the area of VLSI design and I have 6 years of teaching experience.

S. Varalakshmi, Assistant Professor (Adhoc), Department of ECE, JNTUACEP, Pulivendula, A.P, India

G. Krishna Murthy, Assistant Professor (Adhoc), Department of ECE, JNTUACEP, Pulivendula, A.P, India