# 700E Series

# Evaluation Board, Controller & Power CMOS Switch

Ultra-High Speed, High Power, Removable Modules

PRODUCT FLYER July 2017

## **General Description**

The 700 Series Evaluation Board is a complete solution with a Controller and Power CMOS Switch. They are used for demonstrating GaN in Pulsed applications that require both Rise and Fall Times to clock faster than <<200 nsec and Propagation Times of <<200 nsec. The modules are removable for real-world applications when the evaluation phase is complete. Bias adjustment, power sequence, and protection are provided when interfaced to GaN Eval/Test board with minimal inductive & capacitive loads.

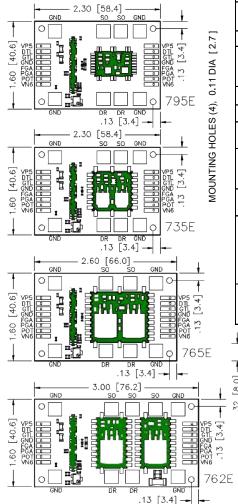

# **Eval Board Configurations**

### **Features**

- Large mounting pads and pitched holes are ideal for banana plug receptacles, headers, & wire jumpers.

- Switch is rated for 100V, Ultra-low Rds ON, Operation up to 150°C, with derated voltage and current.

- Utilize units at half the rated current for best results.

- Controller: Choice of 100L or 200L.

Single power supply. Independent or Sequential Drain and Gate Switching.

- On-board potentiometer for fine gate bias adjustment.

# I/O Pin Descriptions

| LABEL | DESCRIPTION                             |

|-------|-----------------------------------------|

| VP5   | Optional +5V max Supply Voltage.        |

|       | Leave open                              |

| DTL   | Drain Switch Enable TTL Input           |

| GTL   | Gate Switch Enable TTL Input. Usually   |

|       | tied to DTL. Disconnect for independent |

|       | switching                               |

| GND   | Ground                                  |

| FGA   | Fixed Bias Voltage to Transistor Gate   |

| PGA   | Pulsed Bias Voltage to Transistor Gate, |

|       | as enabled by GTL                       |

| РОТ   | Analog Bias Voltage Input. Leave open   |

|       | when trim-pot is utilized. Temp-comp    |

|       | input voltage                           |

| VN6   | Optional -6V max Supply Voltage for     |

|       | Gate bias current boost. Leave open     |

| DR    | High Voltage Output to Transistor       |

|       | Drain. Avoid excess wires or lines to   |

|       | minimize inductive parasitic. Max       |

|       | capacitive load is 500pF for optimum    |

|       | switching speed.                        |

| so    | High Voltage Input Source up to         |

|       | +65VDC. Connect high value storage      |

|       | capacitors here                         |

|       |                                         |

# **Specification Snapshot**

| •                                                |        |        |  |

|--------------------------------------------------|--------|--------|--|

| Parameter                                        | Min    | Max    |  |

| Supply (+) Voltage                               | +20 V  | +65 V  |  |

| Supply (-) Voltage, Optional                     | -6 V   | 0 V    |  |

| Internal (-) Supply V, Gate Pinchoff             | -4.3 V |        |  |

| Internal (-) Supply I                            | -30 mA |        |  |

| Gate Bias Voltage Range                          | -4.3V  | -0.5 V |  |

| Gate Threshold Shutdown Range                    | -3.0 V | -1.0V  |  |

| TTL Voltage Logic High                           | +3.6 V | +5.0 V |  |

| TTL Voltage Logic Low                            | 0 V    | +1.4 V |  |

| Avg Current from MOS peak rating                 |        | 50%    |  |

| MOS Rds ON (40A to 14A)                          | 0.07 Ω | 0.22 Ω |  |

| Drain ON Propagation Delay, cmos                 |        | 150ns  |  |

| Drain ON Rise Time, cmos                         |        | 200ns  |  |

| Drain OFF Propagation Delay, cmos                |        | 250ns  |  |

| Drain OFF Fall Time, cmos                        |        | 200ns  |  |

| Soldering Temp (10 sec)                          |        | +195°C |  |

| Operating Temperature                            | -40°C  | +85°C  |  |

| Storage Temperature                              | -65°C  | +150°C |  |

| Drangation Dalay is massured from 000/ of TTL to |        |        |  |

Propagation Delay is measured from 90% of TTL to 10% of Drain Voltage with device load . Rise/Fall Times are measured at 10% and 90% of signal. Both measurements are summed for total time.

### **Ordering Information**

| Oracing information |                        |  |  |

|---------------------|------------------------|--|--|

| MODEL * ^           | MODULE CONTENT ~ °     |  |  |

| 732E_2R6            | (1) 100X + 332P & 332N |  |  |

| 732E_2R0            | (2) 200X + 332P & 332N |  |  |

| 732E_1R4            | 12A peak, 6A avg max   |  |  |

| 735E_2R6            | (1) 100X + 335CT       |  |  |

| 735E_2R0            | (2) 200X + 335CT       |  |  |

| 735E_1R4            | 12A peak, 6A avg max   |  |  |

| 762E_2R6            | (1) 100X + 362P & 362N |  |  |

| 762E_2R0            | (2) 200X + 362P & 362N |  |  |

| 762E_1R4            | 36A peak, 16A avg max  |  |  |

| 763E_2R6            | (1) 100X + 2 x 362P    |  |  |

| 763E_2R0            | (2) 200X + 2 x 362P    |  |  |

| 763E_1R4            | 36A peak, 16A avg max  |  |  |

| 765E_2R6            | (1) 100X + 365CT       |  |  |

| 765E_2R0            | (2) 200X + 365CT       |  |  |

| 765E_1R4            | 36A peak, 16A avg max  |  |  |

| 792E_2R6            | (1) 100X + 392P        |  |  |

| 792E_2R0            | (2) 200X + 392P        |  |  |

| 792E_1R4            | 8A peak, 4A avg max    |  |  |

| 795E_2R6            | (1) 100X + 395CT       |  |  |

| 795E_2R0            | (2) 200X + 395CT       |  |  |

| 795E_1R4            | 8A peak, 4A avg max    |  |  |

- \* Select (1) 100X or (2) 200X Controller

- ^ All models have provisions for fine adjusting Vgs shutdown threshold to desired level. Refer to 100 or 200 Controller Spec Sheets for more information

- ~ Select preset shutdown at Vgs = -2.6V, -2.0V, or -1.4V

- ° Remove modules at solder melting point of <195°C