# Test Time Efficient Design of 6t Dual Port SRAM Cell

Sejal<sup>1</sup>, Mr.Nagendra Sah<sup>2</sup> <sup>1</sup>Student- M.Tech VLSI Design, <sup>2</sup>Associate Professor <sup>12</sup>Punjab Engineering College (Deemed to be University), Chandigarh

Abstract- Test time is rapidly increasing for Static Random Access Memory. Low test time is a need of the hour. With decreasing, technology node, new failure mechanisms are emerging in CMOS circuits, which need novel techniques of testing. These increased testing techniques create difficulties, especially the area-constrained dual port SRAM cells. March algorithm is the most widely used efficient testing technique for SRAM cells. In this paper, a novel March testing methodology has been proposed to reduce the test time for dual port SRAM cells.. Using the novel March test implementation proposed, for dual port SRAM, an appreciable test time reduction is being achieved, compared to the existing test techniques with the same fault coverage.

## Index Terms- Test time, March test, Dual port SRAM

## I. INTRODUCTION

March algorithm is a widely used testing algorithm because of it's high fault coverage, but it has a very high computational time. A complete March test is given in the "{...}" and each March element is specified in "(...)". represents either an upward addressing order or a downward addressing order. The March test modification for dual port SRAMs has been covered in this work

### A. PROBLEM FORMULATION-MECHANISMS OF FAILURE AND THEIR CORRESPONDING FAULT MODELS:

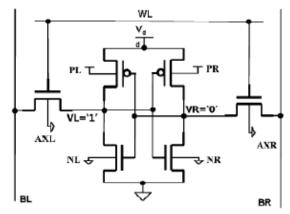

Intra-die variations, resulting from mismatches in parameters of similar transistors (threshold voltage  $V_t$  and geometry L or W ), may lead to new failures in memories.[14,15] The threshold voltage shift of each transistor is considered to be a zero mean Gaussian distribution. Due to its area constraint, a 6-T SRAM[7] is particularly vulnerable to process variations[13]. Mismatch in the six transistors of SRAM cells may result in one of the following conditions.

1) During read operations, comparatively strong access transistors or weak pull-down transistors lead to an increase in the internal node voltage that stores "0" in theSRAM cell. If the pull-up transistor of the cross-coupled inverter is weak, the SRAM cell may flip during the read operation[21]. This is referred as flipping read failure.

2)Comparatively strong pull-up transistors or weak pulldown transistors shift the trip point of the cross-coupled inverters to a higher voltage. This may lead to an unsuccessful write operation of the SRAM cell. This failure is referred to as write failure.

3). Due to excessive mismatch in the cross-coupled inverters, a SRAM cell may lose its value without the cell being accessed by any operations, especially when the supply voltage is lowered to save leakage. This failure is referred to as hold failure.[17]

Fig.1: The 6-T SRAM cell

## II. MARCH ALGORITHM FOR TESTING OF DUAL PORT SRAM

March sequence[9] is used widely for memory testing. It involves applying( writing and reading) patterns to each cell in memory before proceeding to the next cell and the same pattern must be applied to all the cells. This is done in either increasing or decreasing memory address order. March test[15] basically involves the following steps:

- 1. In increasing order of address of the memory cells, write Os to the cells.

- 2. In decreasing order of address of the memory cells, read the cells (expected value 0) and write 1 to the cells.

- 3. In increasing order of address of the memory cells, read the cells (expected value 1) and write 0 to the cells.

- 4. In decreasing order of address of the memory cells, read the cells (expected value 0)

Dual port SRAM cells have their corresponding fault models. They have a higher fault ratio due to the interaction of the aggressor and the victim cell. Two port faults cannot be sensitized using single port fault sensitizations operations. As dual port faults are considered to be a combination of two weak faults. They are divided as faults involving just the

## INTERNATIONAL JOURNAL OF RESEARCH IN ELECTRONICS AND COMPUTER ENGINEERING

A UNIT OF I2OR

victim cell or aggressor cell and the faults involving both aggressor and victim cells. Their broad classification is as shown here in the figure below.

Fig.2 Classification of 2PFs

A better understanding of the 2PF faults can be obtained from the nomenclature shown in the following diagram.

Fig.3 A taxonomy of 2PFs.

A detail of the dual port SRAM faults, along with the ideal march sequence, is presented in the figure below.

## TABLE 1

| List | of | 2PFs; | $x \in$ | $\{0,1\}$ | and $d = \operatorname{don't} \operatorname{care}$ |  |

|------|----|-------|---------|-----------|----------------------------------------------------|--|

| FFM                                  | Fault primitives                                                                   |

|--------------------------------------|------------------------------------------------------------------------------------|

| wDRDF&wDRDF                          | $  < r0 : r0/\uparrow /0 >, < r1 : r1/\downarrow /1 >$                             |

| wRDF&wRDF                            | $< r0: r0 / \uparrow /1 >, < r1: r1 / \downarrow /0 >$                             |

| wRDF&wTF                             | $< r0: w \uparrow /0/->, < r1: w \downarrow /1/->$                                 |

| wCF <sub>ds</sub> &wCF <sub>ds</sub> | $  < w_0 : rd; 0/\uparrow /->, < w_0 : rd; 1/\downarrow /->  $                     |

|                                      | $< w1: rd; 0/\uparrow /->, < w1: rd; 1/\downarrow /->$                             |

|                                      | $  \langle rx: rx; 0/\uparrow/- \rangle, \langle rx: rx; 1/\downarrow/- \rangle  $ |

| wCF <sub>dr</sub> &wDRDF             | $< 0; r0: r0 / \uparrow /0 >, < 0; r1: r1 / \downarrow /1 >,$                      |

|                                      | $< 1; r0: r0/\uparrow /0>, < 1; r1: r1/\downarrow /1>,$                            |

| wCF <sub>rd</sub> &wRDF              | $< 0; r0: r0 / \uparrow /1 >, < 0; r1: r1 / \downarrow /0 >,$                      |

|                                      | $< 1; r0: r0/\uparrow /1 >, < 1; r1: r1/\downarrow /0 >$                           |

| wCF <sub>ds</sub> &wRDF              | $< w0: r0/\uparrow /1 >, < w0: r1/\downarrow /0 >,$                                |

|                                      | $< w1: r0/\uparrow /1 >, < w1: r1/\downarrow /0 >$                                 |

| wCF <sub>ds</sub> &wIRF              | < w0: r0/0/1 >, < w0: r1/1/0 >,                                                    |

|                                      | < w1: r0/0/1 >, < w1: r1/1/0 >                                                     |

| wCF <sub>ds</sub> &wRRF              | < w0: r0/0/? >, < w0: r1/1/? >,                                                    |

|                                      | < w1: r0/0/? >, < w1: r1/1/? >                                                     |

Here CF(coupling faults), RDF(read destructive faults), DRDF(deceptive read destructive faults) have been explained already. The optimum march test sequence for dual port SRAM that has been used for the modification proposed is given here:

$$\{ \begin{array}{ccc} (w0:n) & : & (r0:r0,r0:-) & : & (w1:-) & : \\ M_0 & & M_1 & & M_2 \\ & & (r1:r1,r1:-) & \\ & & M_3 \end{array}$$

March 2PF1-. (optimal version) Fig4 . for Dual Port SRAM

This is the March sequence for maximum fault coverage for detecting two port faults involving single cell with maximum. The corresponding March sequence with maximum fault coverage for two port faults involving 2 cells is given below:

$$\begin{array}{l} \left\{ \begin{array}{l} \left( w0\,;\, w \right) \;;\; \uparrow_{c=0}^{C-1} \; \left( \uparrow_{r=0}^{R-1} \; \left( w1_{r,c}\,;\, r0_{r+1,c},r1_{r,c}\,;\, w1_{r+1,c},w0_{r,c}\,;\, r1_{r+1,c},r0_{r,c}\,;\, w0_{r+1,c} \right) \right) \;; \\ M_0 & M_1 \\ \left( \uparrow_{r=0}^{C-1} \; \left( \uparrow_{r=0}^{R-1} \; \left( w1_{r,c}\,;\, r0_{r,c+1},r1_{r,c}\,;\, w1_{r,c+1},w0_{r,c}\,;\, r1_{r,c+1},r0_{r,c}\,;\, w0_{r,c+1} \right) \right) \; \right\} \\ M_2 \end{array}$$

Fig.5 . March 2PF2<sub>ev</sub> - (optimal version ). for Dual Port SRAM

#### III. PROPOSED MODIFICATION IN MARCH **SEOUENCE**

The prime focus of this work has been to decrease the computation time for testing the dual port 6-T SRAM cell using March Algorithm. In order to solve this problem of high computation time, the march elements mentioned in the figure above have been taken up and the following novel approaches have been implemented in them.

1)A single March element has been divided into a set of distinct operations that are applied on two different memory addresses simultaneously.

2)The simultaneous application is the innovative part that gives a reduction in computation time.

3) To better understand this, let us consider one of the optimized March elements studied above

$\prod \{ \bigcup (w0:n); (r0:r0, w1:r0); (r1:r1, w0:r1) \}$

In order to reduce the computation time, the proposed approach simultaneously implements the two operations by targeting two different memory locations at the same time, one for r0 operation and one for w1 operation. The two different memory locations that are accessed from the topmost and bottommost memory location of the dual port sram, that is there are two loops running to apply the two memory operations; one loop starts from the highest memory location and proceeds towards lower memory locations and one loop starts from the smallest memory location and proceeds towards the higher memory locations. One loop applies (say, in this example) r0 and the other loop applies w1. According to the base paper, [15] the aggressor cell can stimulate a fault in a weak victim cell only if the 2 cells are at immediate neighbouring memory locations. Thus, the 2 memory locations chosen here for simultaneous application of the operations of the march element, do not infringe any basic criteria for detection of faults as neither the aggressor cell nor the victim cell constitute a pair of neighbouring memory locations. The operation stops when the 2 simultaneous loops meet at the center of the memory array. This is the novelty proposed in this thesis work. Codes have been written for performing a march operation and detecting faults if any. A signal "test complete" turns active high, when the march operation

INTERNATIONAL JOURNAL OF RESEARCH IN ELECTRONICS AND COMPUTER ENGINEERING

A UNIT OF I2OR

## IJRECE VOL. 6 ISSUE 2 APR.-JUNE 2018

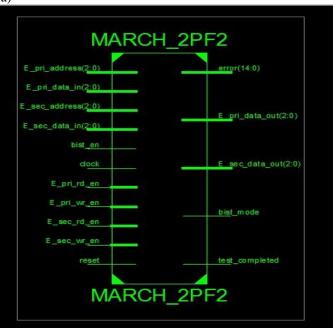

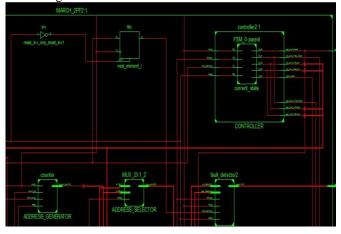

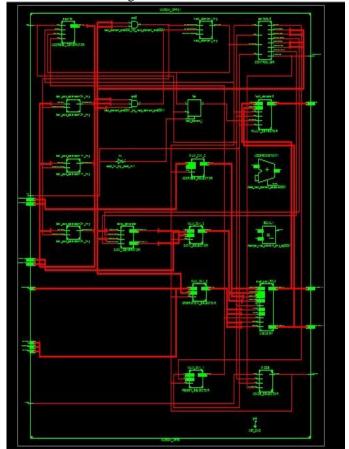

has been performed on the entire dual port SRAM. The test time at which the test\_complete signal goes high, is much reduced using this proposed approach , than the conventional approach to implement the March algorithm. After implementing the design above, the circuit is simulated. The RTL schematic of the circuit is generated. It is shown in the figures below. The timing waveforms of the circuit have been generated. The timing waveforms have been generated for 2 cases-

1) Implementing the standard design of 6-T SRAM cell without the modifications proposed above and

2) Implementing the above proposed computation time efficient 6T SRAM cell.

The signal "test\_comp" clearly depicts an appreciable improvement in the computation time. An improvement of 16.2% is achieved with the design proposed above

## IV. SIMULATIONS AND RESULTS

Based on the approach given above, the design has been implemented on the Xilinx ISE 14.2 and the results are as presented below. Codes have been written for performing a march operation and and detecting faults if any. A signal "test\_complete" turns high, when the march operation for dualport SRAM has been performed on the entire dual port SRAM. The test time at which the test\_complete signal goes high, is much reduced using this proposed approach , than the conventional approach to implement the March algorithm. The results have been shown in the next chapter.

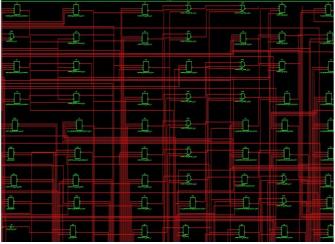

1)The RTL diagram of the SRAM cell is given here:

b)The detailed RTL of any part of RTL diagram is obtained by double clicking on it as shown in the diagram below. The following diagram shows the modules that have been used up in building the 6-T SRAM cell.

c)The detailed RTL diagram, showing all the individual modules, that have been used in the program to make up the cell is shown in the diagram below.

V.

d)The detailed RTL showing the LUTs has been shown in the diagram below.

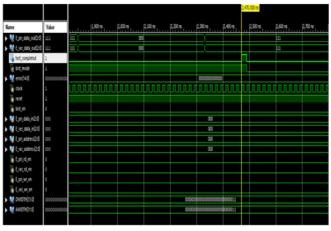

1) a)The following diagram shows the timing waveform of the 6-T SRAM cell, simulated with the conventional approach to implement March algorithm.

test is completed at 2470 ns

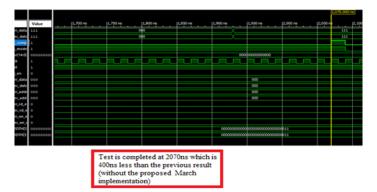

b) The following diagram shows the timing waveform obtained by simulating the 6-T SRAM cell with the proposed implementation of the March algorithm.

As can be seen from the results above, the proposed implementation of march algorithm reduces the test time by 16.9 %, which is an appreciable improvement in reducing the total test time. This increases the overall efficiency of the circuit.

| Table 2: Experimental Results |                |             |  |  |  |  |  |  |  |

|-------------------------------|----------------|-------------|--|--|--|--|--|--|--|

| Test time with                | Test time with | Percentage  |  |  |  |  |  |  |  |

| the existing                  | the proposed   | improvement |  |  |  |  |  |  |  |

| March sequence                | approach for   |             |  |  |  |  |  |  |  |

| fordualport                   | March sequence |             |  |  |  |  |  |  |  |

| SRAM                          | for dualport   |             |  |  |  |  |  |  |  |

|                               | SRAM           |             |  |  |  |  |  |  |  |

| 2470 ns                       | 2070ns         | 16.9%       |  |  |  |  |  |  |  |

## CONCLUSION AND FUTURE SCOPE

With technology scaling, process variations result in functional failures in memory systems. This leads to novel testing techniques, which cause an increased test time. In this work, March test sequence for dual port SRAM has been taken up and modifications have been proposed in the same, to reduce the test time of the SRAM memory cell. Implementing the optimized March test sequence with the approach proposed above, of simultaneously applying the different dual port March elements in ascending and descending order, greatly reduces the test time, as is evident in the results. So this technique is efficient for a reduction in the test time. This also increases the cost effectiveness. Thus, this technique can be efficiently implemented to obtain a high fault coverage with a reduced test time. The results reflect a 16.9 % improvement, using the proposed approach.

Further scope of work in this research work , lies in some domains. Some of them are mentioned here. To reduce the test time, further optimizations in the march test sequence can be done. In this thesis, an optimized March sequence has been used. Optimizations used account both for high faut coverage and reduced test time. Similarly alternative optimizations can be proposed to reduce the test time, like observing the redundancy in some elements and phasing it out. Thus , the topic is promising for future research. The paper showed that the approach generates, 16.9 % improvement that is, efficient results.

### VI. REFERENCES

- Anmol Gulati, Ashutosh Gupta, Shruti Murgai, and Lala Bhaskar," Design and implementation of power efficient 10-bit dual port SRAM on 28 nm technology", AIP Conference Proceedings 1715, 020002 (2016)

- [2]. Anumol K A, N.M.Siva Mangai, P.Karthigai Kumar(2013)," Built in Self Test Architecture for Testing SRAM Using Transient Current Testing" Proceedings of 2013 IEEE

## INTERNATIONAL JOURNAL OF RESEARCH IN ELECTRONICS AND COMPUTER ENGINEERING

A UNIT OF I2OR

Conference on Information and Communication Technologies (ICT 2013)

- [3]. Chih-Long Chang and Iris Hui-Ru Jiang(2013)," Pulsed-Latch Replacement Using Concurrent Time Borrowing and Clock Gating", IEEE Transactions On Computer-Aided Design Of Integrated Circuits And Systems, Vol. 32, No. 2, February 2013

- [4]. Donald T. Wong, R. Dean Adams, Member, Ieee, Arup Bhattacharyya Member, Ieee, James Covino, John A. Gabric, And George M. Lattimore, "An Il-ns 8Kx 18 CMOS Static RAM with 0.5-pm Devices", IEEE Journal of Solid- State Circuits. Vol 23. No 5. October 1988

- [5]. Jente B. Kuang, Jeremy D. Schaub, Fadi H. Gebara, Dieter Wendel, Thomas Fröhnel, Sudesh Saroop, Sani Nassif, and Kevin Nowka(2011), Ieee Transactions On Circuits And Systems—I: Regular Papers, Vol. 58, No. 9, September 2011

- [6]. L. B. Zordan, A. Bosio, L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel, N. Badereddine (2012)," Optimized March Test Flow for Detecting Memory Faults in SRAM Devices Under Bit Line Coupling", Infineon Technologies, France

- [7]. M. H. Tehranipour, Z. Navabi(2000), "zero-overhead bist for internal-sram testing", The 12 International Conference on Microelectronics Tehran, Oct. 31- Nov. 2,2000

- [8]. Mingkun Li, Ning Ma, Shaojun Wang," SRAM FPGAs single event upsets detection method based on selective readback", IEEE Xplore

- [9]. Muddapu Parvathi , N. Vasantha, K. Satya Parasad(2012) ," Modified March C - Algorithm for Embedded Memory Testing", International Journal of Electrical and Computer Engineering (IJECE) Vol. 2, No.5, October 2012, pp. 571~576

- [10].P. Pavan Kumar, Dr. R Ramana Reddy, M.Lakshmi Prasanna Rani," Design Of High Speed and Low Power 4t SRAM", International Journal of Scientific and Research Publications, Volume 5, Issue 2, February 2015 1 ISSN 2250-3153

- [11].Navneet Kaur Saini, Aniruddha Gupta, Ravija Prashar and Parul Gupta(2016)," Low Power Circuit Techniques For Optimizing Power In High Speed SRAMs", Intl. Conference on Advances in Computing, Communications and Informatics (ICACCI), Sept. 21-24, 2016

- [12]. Preston, Ronald P"14: Register Files and Caches" The Design of High Performance Microprocessor Circuits. IEEE Press. p. 290, 2001.

- [13].Qikai Chen, Hamid Mahmoodi, Swarup Bhunia, and Kaushik Roy(2005)," Efficient Testing of SRAM With Optimized March Sequences and a Novel DFT Technique for EmergingFailures Due to Process Variations", IEEE Transactions On Very Large Scale Integration (Vlsi) Systems, Vol. 13, No. 11, November 2005

- [14]. Said Hamdioui, Ad J. van de Goor(2000)," An Experimental Analysis of Spot Defects in RAMs: Realistic Fault Models and Tests", Delft University of Technology

- [15]. Said Hamdioui, Ad J. van de Goor(2002)," Efficient tests for realistic faults in dual port SRAMs", IEEE Transactions on Computers, Vol 51, No. 5, May 2002

- [16] Sanjana S R.; Balaji Ramakrishna S., Samiksha, Roohila Banu, Prateek Shubham, "Design and Performance Analysis of 6T SRAM Cell in 22nm CMOS and FINFET Technology Nodes", International Conference on Recent Advances in Electronics and Communication Technology (ICRAECT), 2017

- [17].Sergei Skorobogatov, "Low temperature data remanence in static RAM". University of Cambridge, Computer Laboratory. Retrieved 2008-02-27., June 2002.

- [18].Seungwhun Paik, Inhak Han, Sangmin Kim, and Youngsoo Shin(2012), "Clock Gating Synthesis of Pulsed-Latch Circuits", IEEE Transactions On Computer-Aided Design Of Integrated Circuits And Systems, Vol. 31, No. 7, July 2012

- [19]. "Tentative Toshiba mos digital integrated circuit silicon gate cmos 4,194,304-word by 16-bit cmos pseudo static RAM" 070731 toshiba.com

- [20]. Zhiyu Liu , Volkan Kursun , "Characterisation of a Novel Nine Transistor SRAM Cell", IEEE Transactions on Very Large Scale Integration (VLSI) Systems  $\cdot$  May 2008

- [21]. Said Hamdioui, Member, IEEE, Zaid Al-Ars, Member, IEEE, Ad J. van de Goor, Member, IEEE, and Mike Rodgers, Member, IEEE," Linked Faults in Random Access Memories: Concept, Fault Models, Test Algorithms, and Industrial Results", IEEE Transactions On Computer-Aided Design Of Integrated Circuits And Systems, Vol. 23, No. 5, May 2004