# AN FPGA BASED PASSIVE K-DELTA-1-SIGMA MODULATOR

by Angsuman Roy Matthew Meza Joey Yurgelon R. Jacob Baker

#### A BRIEF ROADMAP

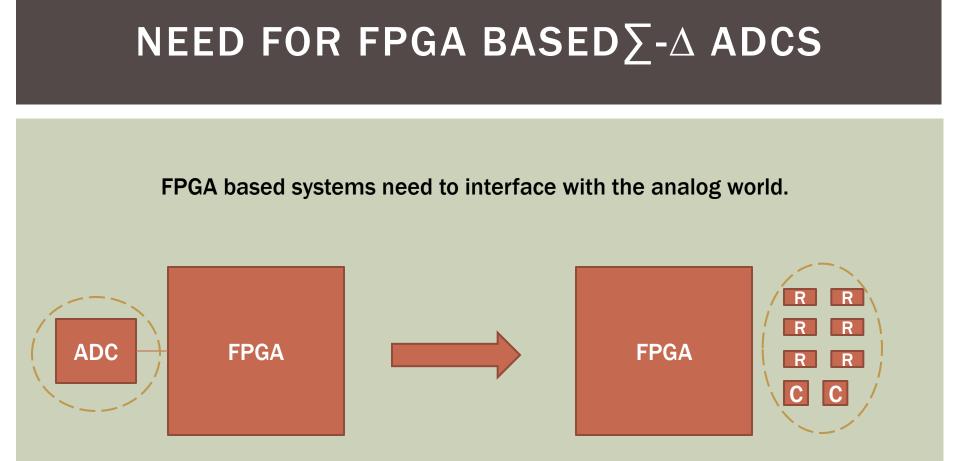

- Need for FPGA Based ADCs

- **Review of Basic**  $\sum -\Delta$  **Principles/Adapting**  $\sum -\Delta$  **ADCs for FPGAs**

- **Proposed KD1S**  $\sum$ - $\Delta$  Modulator Topology

- Circuit Design

- Test Results

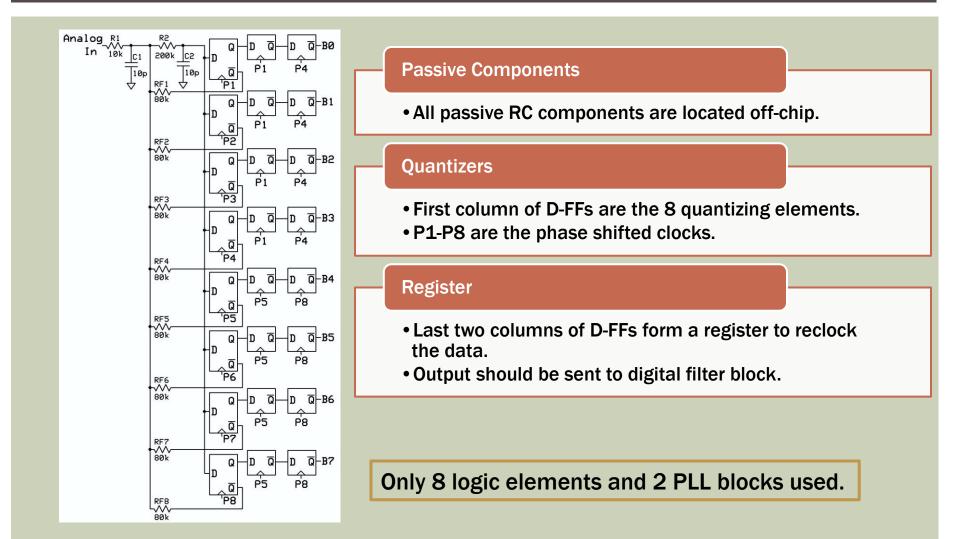

A costly ADC chip can be replaced with a handful of passive components.

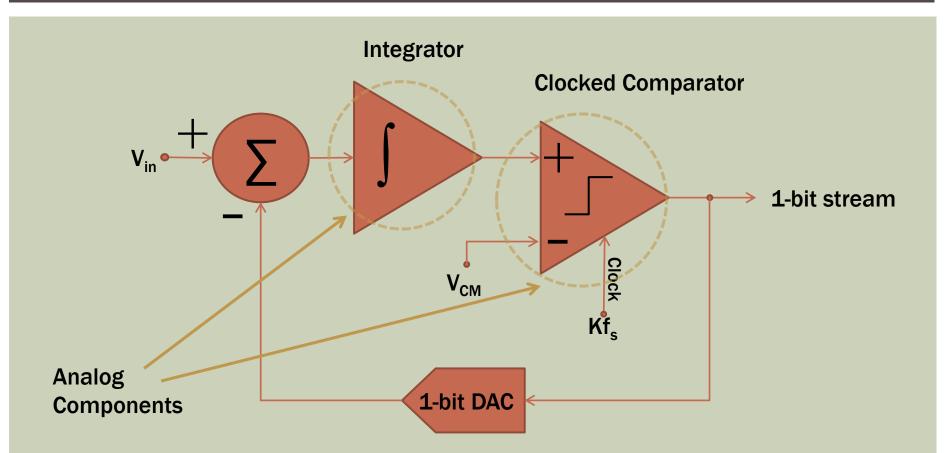

# REVIEW OF BASIC $1^{ST}$ ORDER $\sum -\Delta$ MODULATORS

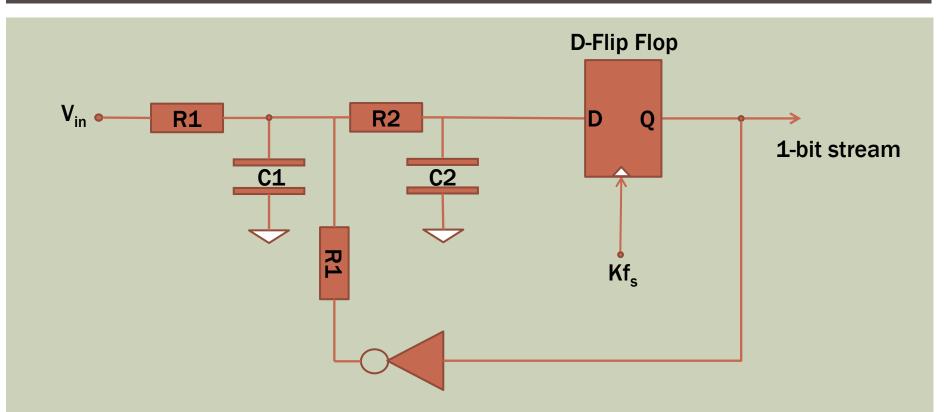

Generally,  $\sum \Delta$  modulators use clocked comparators as the quantizing element which are analog circuits.

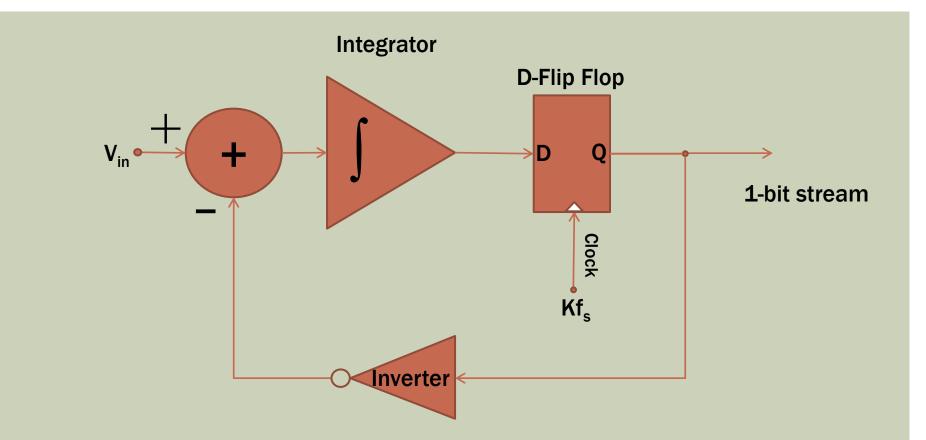

# ADAPTING $\sum -\Delta$ MODULATORS TO FPGAS

The clocked comparator can be replaced with a D-FF and the common mode voltage is replaced by the switching point of the D-FF.

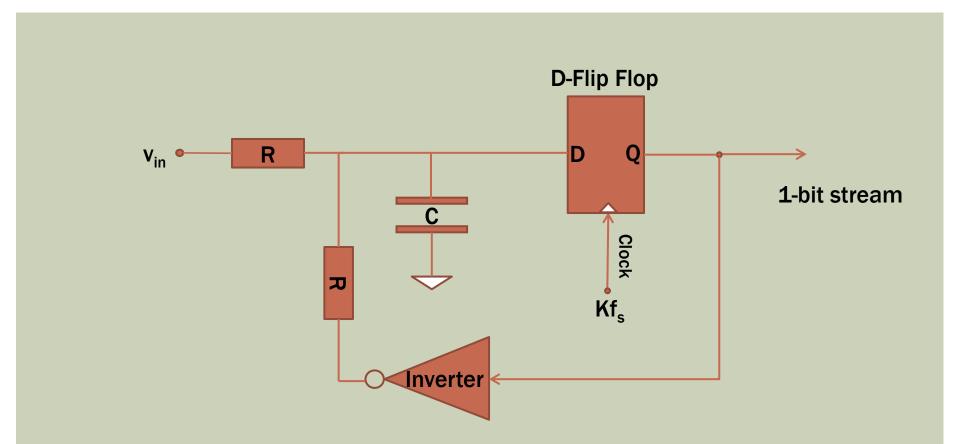

#### **ADDING PASSIVE COMPONENTS**

The integrator and summing block are replaced by passive RC components.

### **IMPROVING THE DESIGN**

Previous work has shown that this particular passive  $2^{nd}$  order  $\sum \Delta$  topology has the best performance.

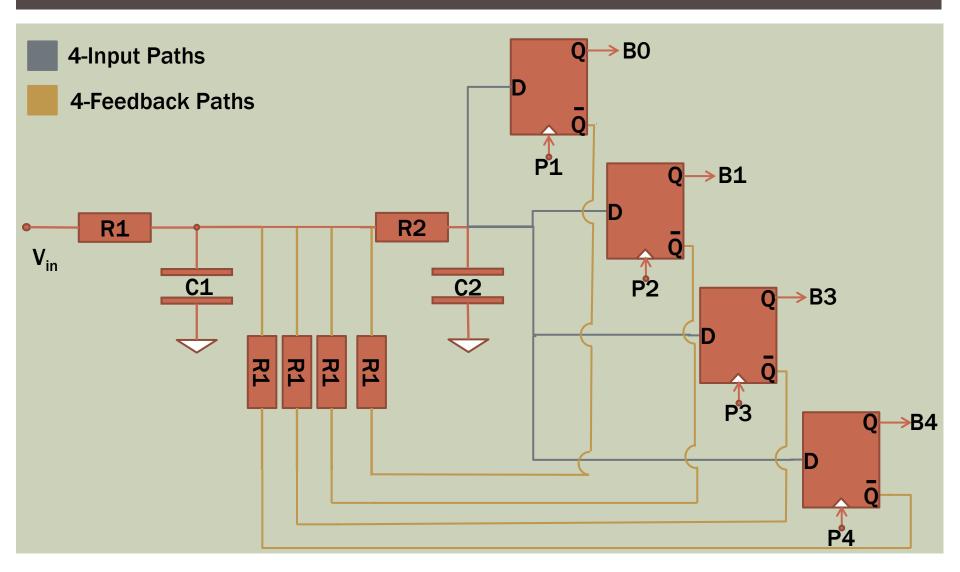

#### K-DELTA-1-SIGMA (KD1S)

#### Requires K Quantizers There are K Feedback Paths Effective

Requires K Clock Signals Effective Sampling Rate is Increased K Times

Only 1 Integrator (Sigma) Required

#### **BASIC EXAMPLE**

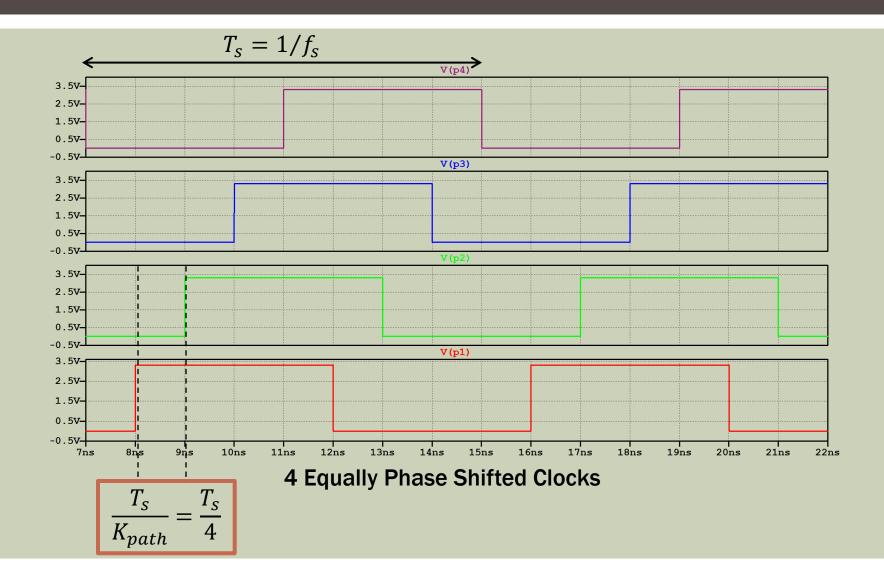

#### CLOCKS

#### USING PLL RESOURCES ON AN FPGA

# Two PLL blocks on an Altera Cyclone IV EP4CE115 FPGA was used to generate 8 phase shifted clocks for our 8 path KD1S Modulator

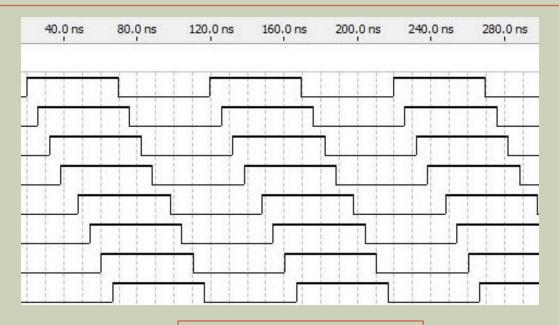

**Simulation in Quartus**

#### SCHEMATIC OF K1DS

### TESTING

#### **Noise Shaping**

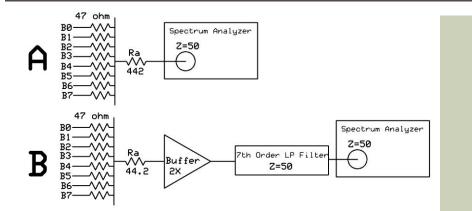

• Test configuration "A" used to examine noise spectrum.

#### Signal to Noise Ratio

• Test Configuration "B" used to measure SNR.

#### Clocks

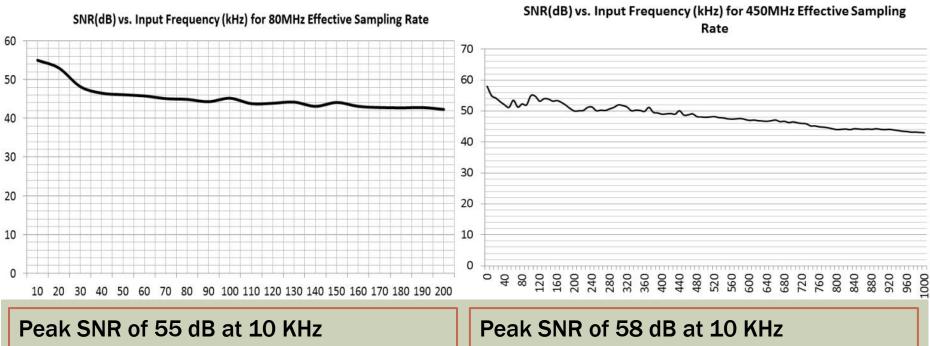

- Tests were done at clock frequencies of 10 MHz and 56.25 MHz.

- Effective sampling rates of 80 MHz and 450 MHz.

#### RESULTS

corresponding to 8.8 effective number of bits (ENOB).

Peak SNR of 58 dB at 10 KHz corresponding to 9.3 effective number of bits (ENOB).

Oversampling ratio (OSR) nominally set to 512.

### **RESULTS SUMMARY**

| Parameter                            | Value                     |

|--------------------------------------|---------------------------|

| Base Clock Frequency                 | 10 MHz / 56.25 MHz        |

| Effective Sampling<br>Rate           | 50 MHz / 450 MHz          |

| Peak SNR                             | 55 dB / 58 dB             |

| ENOB                                 | 8.8 bits / 9.3 bits       |

| Logic Element Use                    | 8                         |

| PLL Use                              | 2 (4 total on chip)       |

| Percentage of Logic<br>Elements Used | 0.007% (8 out of 114,480) |

| I/O Pin Use                          | 9                         |

#### CONCLUSION

Expensive ADC chip can be replaced by a few passive components. Sampling rates into the 10s of GHz should be possible with modern FPGAs.

Complex digital filtering can be performed on the FPGA.

Very low resource utilization.

Nominal 10-bit ADC can be implemented on FPGA.