# 300PNC Series CMOS Power Switch

For Ultra-High Speed Pulsed GaN Systems

PRODUCT FLYER July 2017

#### **General Description**

The Complementary MOSFET Switches of the 300PNC Series offers highperformance with ease of integration. Designed for Pulsed-mode, they have clocked speeds of <<200nsec for Rise and Fall Times. Its compact footprint allows direct placement near the RF Choke of the GaN drain. The MOSFETs on board are rated up to 36A Peak. and are safe from 3X the momentary current surges. With modular design introducing higher thermal resistance, the average current ceiling should be specified at half the rating. These switches are ideally driven by the 100 or 200 Series Controllers.

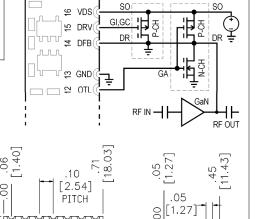

**Typical Connection Diagram**

.09

[2.24]

[13.72]

[2.05]

[13.39]

.10 [2.54]

.06

[1.40]

.38 [9.55]

.06

[1.40]

.36 [9.17]

#### **Features**

- Rated for 100V

- Ultra-low Rds ON

- Operation up to 125°C, with derated voltage and current.

- Total switching times of <500 nsec when used together with 100 or 200 Series Controllers.

- Complementary P & N-channel MOS achieve Rise & Fall Times of <<200ns.</li>

- Identical I/O Ports at opposite sides.

OR

RoHS\* Compliant

100X, 200X CONTROLLER

[1.27

.35

[8.89]

.05 [1.27

.05<sup>-</sup> [1.27]

[17.15]

[2.54]

.00

## **Specification Snapshot**

| Parameter                                                  | Min    | Max    |

|------------------------------------------------------------|--------|--------|

| Source Voltage (SO)                                        | +20 V  | +65 V  |

| Drain Voltage (DR)                                         | +20 V  | +65 V  |

| Gate Voltage (GI) Open Drain                               | 0 V    | +20 V  |

| Gate Voltage (GA) TTL High                                 | +2.0 V | +5.0 V |

| Gate Voltage (GA) TTL Low                                  | 0 V    | +0.8 V |

| Rds ON (12A Peak Switch)                                   |        | 0.22 Ω |

| Rds ON (36A Peak Switch)                                   |        | 0.07 Ω |

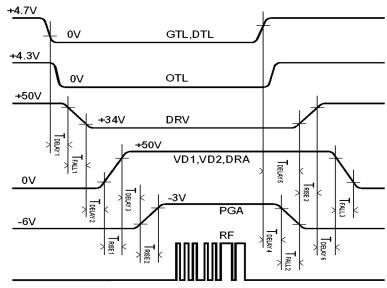

| Turn-ON Prop Delay (T_Delay 2)                             |        | 100 ns |

| Turn-ON Rise Time (T_Rise 1)                               |        | 70 ns  |

| Turn-OFF Prop Delay (T_Delay 6)<br>Complementary Pair Only |        | 150 ns |

| Turn-OFF Fall Time (T_Fall 3)                              |        | 100 ns |

| Period for Pulsed Signals                                  |        | 5 ms   |

| Duty Cycle for Pulsed Signals                              |        | 20 %   |

| Soldering Temp (10 sec)                                    |        | +260°C |

| Operating Temperature                                      | -40°C  | +85°C  |

| Storage Temperature                                        | -65°C  | +150°C |

Propagation Delay is measured from 90% of Drive Signal from Controller to 10% of Drain Voltage Output with load of  $1K\Omega$ . Faster speeds occur with decreased load resistance. Rise/Fall Times are measured at 10% and 90% of signal. Both measurements are summed for total time

# Ordering Information

|          | 0                                                           |

|----------|-------------------------------------------------------------|

| 332P0000 | 12A PEAK, 6A AVG MAX, PULSED                                |

| 332N0000 | COMPLEMENTS 332P ONLY                                       |

| 335CT000 | 12A PEAK, 6A AVG MAX, PULSED                                |

| 362P0000 | 36A PEAK, 16A AVG MAX, PULSED                               |

| 362N0000 | COMPLEMENTS 362P ONLY                                       |

| 365CT000 | 36A PEAK, 16A AVG MAX, PULSED                               |

| 392P0000 | 8A PEAK, 4A AVG MAX, PULSED                                 |

| 395CT000 | 8A PEAK, 4A AVG MAX, PULSED<br>SWITCH POWER CMOS, TTL DRIVE |

#### Switch I/O Pin Descriptions

<u>GA</u> is a gate input that receive TTL signals only from OTL output of Controller. Extra caution should be taken when handling TTL signals to prevent damage.

$\underline{\mathbf{GI}}$  is a gate input connected to DRV of Controller. These ports are interconnected for P & N-Chan Pairs. For a Single Switch module  $\underline{\mathbf{GI}}$  is tied to  $\underline{\mathbf{GC}}$ .

<u>GC</u> is interconnected to like ports for P & N-Chan Pairs. It is only tied to <u>GI</u> for a Single Switch configuration.

<u>GV</u> is interconnected to like ports for P & N-Chan Pairs. Otherwise, leave port open for a Single Switch configuration.

<u>DR</u> are drain outputs that connect to the GaN device drain. Switching speeds may be compromised when bypass capacitance exceeds 500pF.

<u>SO</u> are source inputs that take up to +65V supply. Larger storage capacitance are attached here.

NC is no connection.

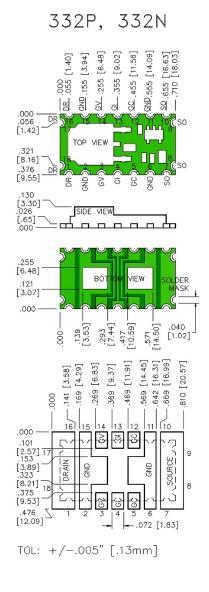

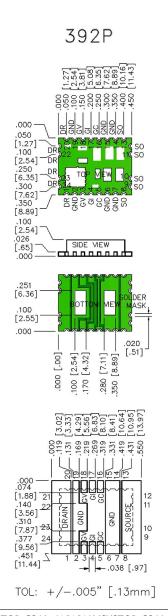

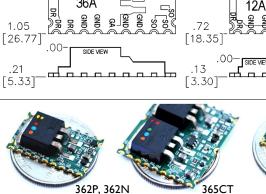

### Outline & Land Pattern

362P, 362N

**Typical Timing Diagrams**

Refer to Application Note XAN-2 for further details.