# Low Power and High-Speed Optimization of FinFET Based Mixed Logic 4TO16 Inverted Decoder

Mohitsharma<sup>1</sup>, Rajesh Kumar<sup>2</sup>

<sup>1</sup>M.tech Scholar, ECE, SachdevaInstitute of Technology, Farah Mathura, India <sup>2</sup>Assistant Professor, SachdevaInstitute of Technology, Farah Mathura, India

Abstract- In this paper, we introduce a mixed-logic design method with the use of FinFET technology for line decoders 2 to 4 and 4 to 16 mode, combining the basic transmission gate logic, the pass transistor dual-value logic and base CMOS logic. To configurations are studied and analyzed which are 14T and 15T, 14T is for low power and low transistor count benefit and 15T is for high performance in terms of power and delay. FinFET comes out to be excellent substitute of bulk MOSFET. Also, according to researchers the short channel effects are basically reduced in FinFET, the results of the decoders are compared with the MOSFET counterpart. The technology nodes taken is 32nm as short channel effects increase the power consumption and unnecessary switching in the circuit. It is seen that the power, PDP and Voltage Source Power Dissipation are improved in the circuit by about 97%, 98% and 99% respectively with same but lower delays.

Keywords- Decoder, FinFET, Short Gate, Power.

### I. INTRODUCTION

Static CMOS circuits are utilized for most by far of logic gates in incorporated circuits. [1]They comprise of correlative nMOS pull down and pMOS pull up systems and present great execution just as protection from commotion and gadget variety. In this way, CMOS logic is described by power against voltage scaling and transistor estimating and accordingly dependable task at low voltages and little transistor sizes. [2] Information signals are associated with transistor gates just, offering decreased plan unpredictability and assistance of cell-based logic blend and structure. Passtransistor logic was primarily created during the 1990s, when different structure styles were presented, planning to give a feasible option to CMOS logic and improve speed, power and zone. [3][4] Its primary plan distinction is that inputs are connected to both the gates and the source/drain dispersion terminals of transistors. Pass transistor circuits are actualized with either individual nMOS/pMOS pass transistors or parallel sets of nMOS and pMOS called transmission gates. This work builds up a mixed-logic plan approach for line decoders, joining gates of various logic to a similar circuit, with an end goal to get improved execution contrasted with single-style structure. [5] Line decoders are major circuits, generally utilized in the fringe hardware of memory exhibits (for example SRAM), multiplexing structures, usage of Boolean logic capacities and different applications. Regardless of their significance, a generally little measure of writing is devoted to their streamlining, with some ongoing work including and a method to propose a better technique is presented. [6][11]

#### **FinFET and Decoders:**

FinFETs are a vital advance in the development of semiconductors since mass CMOS experiences issues in scaling past 32 nm. Utilization of the back gate prompts very intriguing plan openings. [7] Rich decent variety of configuration styles, made conceivable by free control of FinFET gates, can be utilized successfully to decrease absolute dynamic power utilization IG/LP mode circuits give an empowering tradeoff among power and zone. In these theories, 2:4 decoders is talked about with 14 transistor and 15 transistor LP, LPI, HP and HPI in present situation, power decrease is a noteworthy issue in the technology world. The low power configuration is serious issue in superior computerized framework, [1][8] for example, chip, advanced flag processors (DSPs) and different applications. The chip thickness and higher working pace prompts the arrangement of astoundingly complex chips with high clock frequencies. In this way, arranging of low power VLSI circuits is a mechanical need in these in light of the prominence for minimized buyer machinesgadget. [12] [10] In a microchip/microcontroller-based system, the most customarily used square is the bearing set decoder. In this way; it will be not wrong in case we state the bearing set decoder uses more power. Along these lines overhauling the vitality of this square will be valuable to diminish the general power use of the system. Along these lines, proposed plan for this theory is the utilization of FinFET system to diminish power utilization of guidance decoder. [14][15] In this proposition, we have proposed the structure of 2:4 decoder with the utilization of FinFET logic to lessen the power of the decoder and subsequently will help in power decrease of generally framework.

#### **Simulation Results:**

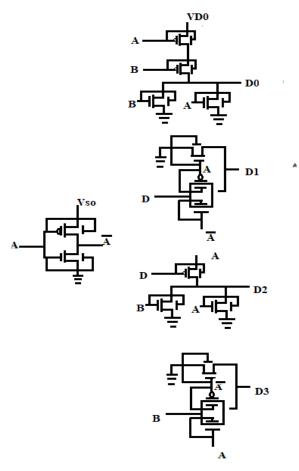

Figure 1 shows a two input 2 to 4 decoder using FINFET Technology in 32nm in SG Mode. In short gate mode the back gate is connected to the front gate. The main important parameters in logic circuit design are HFIN, TFIN and NFIN which are basically Height of Fin, thickness of fin and number of fins, the number of fins we selected are 2 and TFIN is 10n, HFIN is 5n in all the circuits.

## IJRECE VOL. 7 ISSUE 2 (APRIL- JUNE 2019)

Fig.1: Two-input 2 to 4 decoder using FINFET

Fig.2: Two-input 2 to 4 decoder Technique using FINFET

Figure 2 shows a two input 2 to 4 decoder using FINFET Technology in 32nm in SG Mode. This figure is for the 15 T in which the DO part is basically in CMOS logic and others in DVL/TGL mixed valued logics.

## ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE)

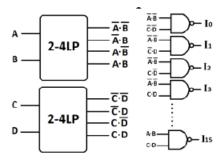

Fig.3: Proposed 4 to 16 decoder based on FinFET

Figure 3 shows Proposed 4 to 16 decoder based on FinFET Technology. The short gate decoders in 14t and 15t mode are then used for making inverted 4 to 16 decoder based on FinFETs, as seen in the figure 3 and 4 the NAND gates are used in cmos logic for FinFETs. To obtain the 16 outputs I0 to I16.

Fig.4: Proposed 4 to 16 decoder based on FinFET

Figure 4 shows Proposed 4 to 16 decoder based on FinFET Technology in High Performance mode, the working I same as of the MOSFET counterpart as discussed earlier.

# II. SIMULATION RESULTS

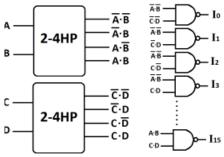

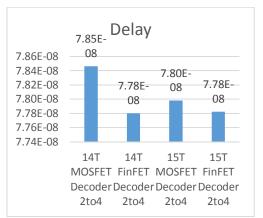

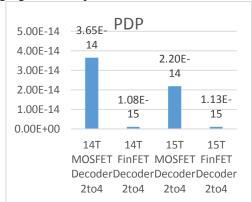

Figure 5, 6 shows the Average Power Comparison and Delay Comparison between different techniques as mentioned below in the figure. It shows the improvement in FinFET based circuits.

Fig.5: Average power in between 14T MOSFET Decoder 2 to 4 to 15 T FinFET Decoder 2 to 4

#### IJRECE VOL. 7 ISSUE 2 (APRIL- JUNE 2019)

Fig.6: Delay in between 14T MOSFET Decoder 2 to 4 to 15 T FinFET Decoder 2 to 4

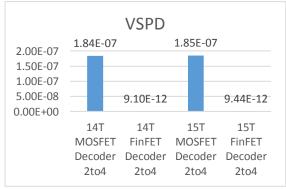

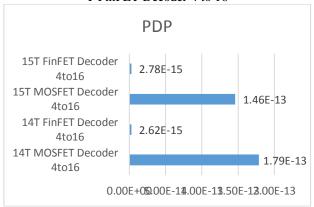

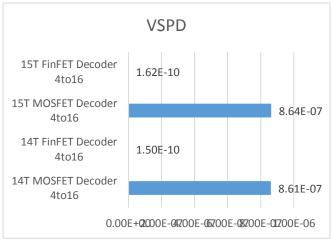

In Figure 7 and Figure 8 shows the comparison of PDP and Voltage Source Power Dissipation of the circuits in 14T and 15T modes shows lower values in FInFET based circuits showing significant improvement in the circuits.

Fig.7: PDP in between 14T MOSFET Decoder 2 to 4 to 15 T FinFET Decoder 2 to 4

Fig.8: VSPD in between 14T MOSFET Decoder 2 to 4 to 15 T FinFET Decoder 2 to 4

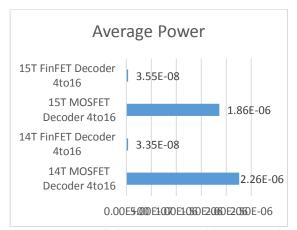

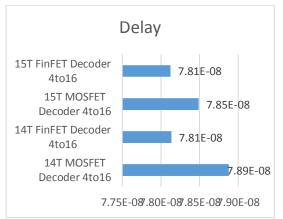

Now, similarly in Figure 9 and Figure 10 shows the improvement in 4 to 16 FinFET circuits based on Average Power Consumption and Delay.

#### ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE)

Fig.9: Average power in between 14T MOSFET Decoder 4 to 16 to 15 T FinFET Decoder 4 to 16

Table 1: simulation result

|         | 14T                      | 1.400                             |                          |                                   |

|---------|--------------------------|-----------------------------------|--------------------------|-----------------------------------|

|         | 171                      | 14T                               | 15T                      | 15T                               |

|         | MOSFET                   | FinFET                            | MOSFET                   | FinFET                            |

|         | Decoder                  | Decoder                           | Decoder                  | Decoder                           |

|         | 2to4                     | 2to4                              | 2to4                     | 2to4                              |

| Average |                          | 1.38E-                            |                          | 1.45E-                            |

| Power   | 4.65E-07                 | 08                                | 2.82E-07                 | 08                                |

|         |                          | 7.78E-                            |                          | 7.78E-                            |

| Delay   | 7.85E-08                 | 08                                | 7.80E-08                 | 08                                |

|         |                          | 1.08E-                            |                          | 1.13E-                            |

| PDP     | 3.65E-14                 | 15                                | 2.20E-14                 | 15                                |

|         |                          | 9.10E-                            |                          | 9.44E-                            |

| VSPD    | 1.84E-07                 | 12                                | 1.85E-07                 | 12                                |

|         | 14T                      | 14T                               | 15T                      | 15T                               |

|         | MOSFET                   | FinFET                            | MOSFET                   | FinFET                            |

|         | Decoder                  | Decoder                           | Decoder                  | Decoder                           |

|         | 4to16                    | 4to16                             | 4to16                    | 4to16                             |

| Average |                          | 3.35E-                            |                          | 3.55E-                            |

| Power   | 2.26E-06                 | 08                                | 1.86E-06                 | 08                                |

|         |                          | 7.81E-                            |                          | 7.81E-                            |

| Delay   | 7.89E-08                 | 08                                | 7.85E-08                 | 08                                |

|         |                          | 2.62E-                            |                          | 2.78E-                            |

| PDP     | 1.79E-13                 | 15                                | 1.46E-13                 | 15                                |

|         |                          | 1.50E-                            |                          | 1.62E-                            |

|         |                          | 1.002                             |                          |                                   |

|         | 14T<br>MOSFET<br>Decoder | 14T<br>FinFET<br>Decoder<br>4to16 | 15T<br>MOSFET<br>Decoder | 15T<br>FinFET<br>Decoder<br>4to16 |

In table 1, all results are shown in tabulated form.

#### IJRECE VOL. 7 ISSUE 2 (APRIL- JUNE 2019)

Fig.10: Delay in between 14T MOSFET Decoder 4 to 16 to 15 T FinFET Decoder 4 to 16

Fig.11: PDP in between 14T MOSFET Decoder 4 to 16 to 15 T FinFET Decoder 4 to 16

In above Figure 11 and below Figure 12 PDP and Voltage source power dissipation are shown compared to the Mos counter circuits.

Fig.12: VSPD 14T MOSFET Decoder 4 to 16 to 15 T FinFET Decoder 4 to 16

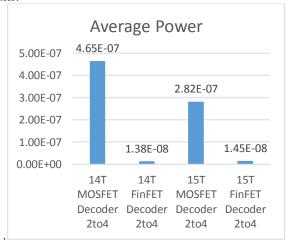

#### III. CONCLUSION

The use of FinFET over MOSFET in the proposed technique reduces Average Power consumption; it indicated that FinFET is a promising substitute for MOSFET beyond 32nm technology. The reduced short channel effects in FinFET and

# ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE)

better control over the gate of the FinFET improves the Average Power in designed techniques.97% improved in 14T 2to4 decoder on Average Power, while giving almost same and lower delay, 97% better in terms of PDP and 99% better in terms of VSPD. 96% improved in 15T 2to4 decoder on Average Power, while giving almost same and lower delay, 94.8% better in terms of PDP and 99.9% better in terms of VSPD. 98.5% improved in 14T based 4to16 decoder on Average Power, while giving almost same and lower delay, 98.5% better in terms of PDP and 99.9% better in terms of VSPD. 98% improved in 15T based 4to16 decoder on Average Power, while giving almost same and lower delay, 98.0% better in terms of PDP and 99.9% better in terms of VSPD.

#### IV. REFERENCES

- D. Balobas et. Al. "Design of Low Power, High Performance 2-4 and 4-16 Mixed-Logic Line Decoders" 1549-7747 (c) pp. 1549-7747 2015 IEEE.

- [2]. Kazuo Taki "A Survey for Pass-Transistor Logic Technologies" Kobe University

- [3]. Pooja Verma et. Al. "An Optimize Approach to Design MUX Based Decoder Using Source Coupled Logic" ISSN: 1738-9968 IJHIT pp. 285-292 2016.

- [4]. B. Madhuri et al. "Design of Low-Power High-Performance 2-4 and 4-16 Mixed-Logic Line Decoders" IJPRES Volume 9 /Issue 5 / MAR pp-282-292 2018.

- [5]. D Komali et al. "Design of Low-Power High-Performance 2-4 and 4-16 Mixed Logic Line Decoders" /IJIRCCE. pp.1613-1619 2018.0602076

- [6]. P.Ramakrishna et al. "DESIGN OF LOW POWER HIGH PERFORMANCE 4 -16 MIXED LOGIC LINE DECODER" ISSN (PRINT): 2393-8374, (ONLINE): 2394-0697, VOLUME-5, ISSUE-4, pp. 344-349 2018

- [7]. SOUMEN MOHAPATRA "An Optimization of 16×16 SRAM Array for Low Power Applications" Rourkela pp.28-39 2015

- [8]. Y. Syamala et al. "DESIGN OF LOW POWER CMOS LOGIC CIRCUITS USING GATE DIFFUSION INPUT (GDI) TECHNIQUE" (VLSICS) Vol.4, No.5, October pp.90-95 2013

- [9]. G. Deepika et al. "A LOW POWER CMOS ANALOG CIRCUIT DESIGN FOR ACQUIRING MULTICHANNEL EEG SIGNALS" (VLSICS) Vol.6, No.1, February pp.25-37 2015

- [10]. Saikiran Sudhakar et al. "A New Approach for Low Power Decoder for Memory Array" Indian Journal of Science and Technology 2 Vol 9 (29) | August pp.2-4 2016

- [11]. Pranay Kumar Rahi et al. "DESIGN AND SIMULATION OF 2–TO-4 DECODER USING 32nm, 45nm AND 65nm CMOS TECHNOLOGY" (IJSRET), ISSN 2278 0882 Volume 4, Issue 3, March pp.270-273 2015

- [12].Neil H. E. Weste et al. "CMOS VLSI Design A Circuits and Systems Perspective" Addison-Wesley pp.61-95 2011

- [13].M.Nirmala et al. "Design of Low Power, High Performance 2-4 and 4-16 Decoders by using GDI methodology" IJEECS ISSN 2348-117X Volume 6, Issue 12 December pp.392-397 2017

- [14].Ku. Priyanka et al. "DESIGN OF LOW-POWER 2–4 MIXED-LOGIC LINE DECODERS WITH CLOCK BASED TECHNIQUE" IRJET Volume: 05 Issue: 05 | May-pp.2785-2789 2018

- [15]. D. Markovic et al. "A general method in synthesis of passtransistor circuits" Microelectronics Journal 31 (2000) pp.991– 998