# VLSI Architecture for Transpose Form FIR Filter using Integrated Module and Brent Kung Adder

Kriti Jain M. Tech. Scholar Dept. of Electronics and Communication, SIRT, Bhopal

Abstract— The main objective of this research paper is to design architecture for finite impulse response (FIR) filter based on multiplier-less (Multi-L) by rectifying the problems in the existing method and to improve the speed by using the Brent kung adder (BKA). The Multi-L technique is based on buffer; look up table and shifting based adder technique. This paper is presents in 8 & 16-tap FIR using Multi-L and BKA. The problem of existing architecture is reduced by removing bits from the remainders. The proposed algorithm is implementation Xilinx software Vertex device family.

#### Keywords: - BKA, FIR, Multi-L, Buffer, LUT

#### I. INTRODUCTION

Pipelining turns into a piece of each calculation circuits utilized today from customer items to hand held gadgets. Pipelining is a plan strategy utilized in the majority of the computational units to improve the exhibition what's more, speed. Flip-flops structure the essential components of pipelining and synchronize the information stream during calculation. Ordinarily a D flipflop with low inactivity what's more, low power utilization is utilized in pipeline plan. The pipeline sequencing tasks are constrained by the clock input. So the speed is relative to pipeline stages and the clock. Inability to peruse information or compose a information prompts overwriting or different perusing of similar information. The region involved additionally increments as the quantity of stages increment. So as to improve the presentation of the pipelining, another structure strategy with better blunder dealing with capacity, littler planning punishment, less region and power productive is proposed in this work [1].

The fundamental commitments are planning another flip-flop which receives the working standard of auto gating and shadow locking for pipelining. The flip-flop is equipped for time obtaining and low power utilization. The other commitment is structuring another pipelined design utilizing parallel preparing with part sharing technique. The progression in VLSI innovation and Application Specific Coordinated Circuits (ASIC) have improved the plan for applications like modems, superior quality TV, biomedical framework, advanced sound and so on. In this data age, new ASIC chips are rehashed for rapid, smaller than normal furthermore, low power application. Continuously there is growing a requirement for new plans to consolidate a total Prof. Navneet Kaur Associate Professor Dept. of Electronics and Communication, SIRT, Bhopal

framework in a chip. The execution of DSP calculations in VLSI configuration made frameworks computationally speeder and power productive [2].

A few VLSI based DSP applications are not just worried about the processing yet in addition engaged with transmission or capacity. The new VLSI innovation circuit configuration is frequently appropriate to execute any DSP calculation. The execution is in fact possible and monetarily reasonable. The VLSI circuit plan of the DSP calculation segments builds the exhibition and is savvy when the number of circuits to be produced in enormous, or when the important exhibition necessities are high to the point that they can't be met with some other innovation.

Advances in VLSI innovation additionally open new regions for DSP systems, such as Bio-signal examination, savvy figuring, smaller than normal sensors, robot vision, furthermore, computerization. To investigate VLSI innovation ideally, it is essential that the structure group spread all parts of the plan, detail, DSP calculation, framework, circuit, engineering, rationale and incorporated circuit plan. The issue of planning particular reason DSP frameworks is an intriguing examination theme, yet, increasingly significant, it has noteworthy mechanical and business importance. Numerous DSP frameworks are delivered in extremely huge numbers and require high performance circuits regarding throughput [3, 4]. Despite the fact that the quality decrease strategy has its own favorable circumstances, the issue with the equivalent is the expansion in the basic way. This limits the necessary throughput. This makes issue in high piece applications. These issues can be explained by Look-ahead change. In high piece rate applications the issue is as yet higher and can be explained utilizing parallelism. Recursion in Boolean condition can sort the issues however execution through writing computer programs is less powerful. Along these lines, the Look-ahead change is a powerful strategy to actualize parallelism to VLSI implantations of DSP calculations. The look-ahead changes works with any perplexing reliance diagrams and contrast conditions is present. This change alongside fine-grain pipelining shows better execution [5].

## IJRECE VOL. 7 ISSUE 4 OCT.-DEC 2019

#### II. BACKGROUND

The other significant change system used to limit the number of useful squares in DSP engineering blend is collapsing. The guideline behind collapsing is in opposition to unfurling where the unit-time handling is changed to N unit times preparing with a collapsing variable of N. In this way, different same tasks (not as much as N) utilized in unique framework has been supplanted with a solitary activity obstruct in changed framework. Along these lines, in N unit-times, a practical square in changed framework could be reused to perform N activities in unique framework [6].

The other use of collapsing change is the assurance of control circuits where numerous calculation tasks are time-multiplexed to a solitary useful unit. As the equipment is diminished by a factor of N, the time is expanded by a similar factor. This prompts enormous number of registers, so enrolls minimization methods is required. The main weakness of collapsing is that it needs more memory component to store the impermanent information. The explanation is that numerous information delivered from an activity square should be recognized from N information created from unique activities. The prominently utilized strategy to accomplish higher working velocity is pipelining in a few applications, for example, Digital Signal Processing (DSP) frameworks, microchips, and so on. It begins from the possibility of a water pipe with ceaseless water sent in without sitting tight for the water in the pipe to turn out [7].

As needs be, it brings about speed improvement for the basic way in most DSP frameworks. For instance, it can either build the clock speed or decrease the control utilization at a similar speed. In DSP application circuits the pipelining decreases the basic way. Pipelining is executed to lessen the basic way delay by utilizing pipelining registers. These pipelining registers are embedded between the rationale also, number juggling circuits. In engineering level pipelining, the registers are embedded in the middle of the combinational squares or number juggling circuits, however the wanted preferred position happens just if the addition is done at the opportune spot [8].

Simultaneously the procedure of basic way decrease throughput per clock ought not be influenced. The decrease of calculation time is finished by evaluating the planning models of the adders and multipliers. Since the registers are embedded at the neighboring segment in the data path timing models are evaluated. In flag and picture preparing calculations like discrete cosine change, discrete wavelet change, quick Fourier change, FIR channels a enormous number of adders and multipliers are required. The multipliers utilized in Duplicate Accumulate Unit (MAC) and multi operand units comprise the basic way delay. Despite the fact that in writing a few multipliers and adders are planned with quick calculation and less power the information way needs alteration. In consistent pipelining the registers not just set in the middle math circuits however can be inside the circuits itself [9].

# ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE) III. DISTRIBUTIVE ARITHMETIC TECHNIQUE

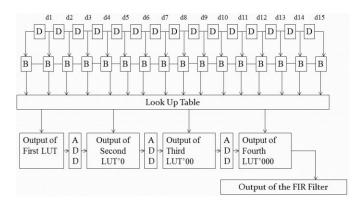

Appropriated number-crunching is a significant calculation for DSP applications. It depends on somewhat level improvement of the duplicate and amasses activity to supplant it with set of expansion and moving tasks. The fundamental activities required are an arrangement of table queries, augmentations, subtractions and movements of the info information succession. The LUT stores all conceivable incomplete items over the channel coefficient space [10].

Accepting coefficients h[n] is known constants, and afterward y[n] can be revised as pursues:

$$y[n] = \sum_{n=0}^{N-1} h[n] x[n]$$

(1)

Variable x[n] can be spoken to by:

$$x[n] = \sum_{b=0}^{B-1} x_b[n] 2^b$$

(2)

$$\chi_b[n] \in [0,1]$$

Where  $\chi_b[n]$  the b<sub>th</sub> bit of x [n] and B is the information width, finally, the inner product can be rewritten as follows:

$$y[n] = \sum_{b=0}^{B-1} h[n] x_b[n] 2^b$$

(3)

$$=h[0](x_{B-1}[0]2^{B-1} + x_{B-2}[0]2^{B-2} + x_0[0]2^{0}) + h[1](x_{B-1}[1]2^{B-1} + x_{B-2}[1]2^{B-2} + x_0[1]2^{0}) + ......h[N-1](x_{B-1}[N-1]2^{B-1} + x_{B-2}[N-1]2^{B-2} + x_0[N-1]2^{0}) (4)$$

$$= h[0](x_{B-1}[0] + h[1]x_{B-1}[0] + h[N-1]x_{B-1}[N-1]2^{B-1}) + h[1](x_{B-2}[1] + \dots + h[n-1]x_{B-2}[N-1]2^{B-2}) + \dots + h[0](x_0[0] + x_0[1] + \dots + h[N-1]x_0[N-1]2^0)$$

(5)

$$y[n] = \sum_{b=0}^{B-1} 2^b \sum_{n=0}^{N-1} h[n] x_b[n]$$

(6)

Where n=0, 1... N-1 and b=0, 1... B-1

The coefficients in the majority of DSP applications for the increase accumulate operation are constants.

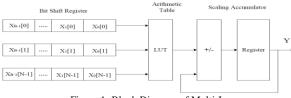

Figure 1: Block Diagram of Multi-L

#### IJRECE VOL. 7 ISSUE 4 OCT.-DEC 2019

### IV. PROPOSED METHODOLOGY

Clock gating is a transcendent procedure utilized for control sparing. It is seen that the normally utilized amalgamation based gating still leaves a huge measure of repetitive clock beats. Information driven gating plans to impair these. To diminish the equipment overhead included, flip-flops (FFs) are assembled so that they share a typical clock empowering signal. The clock gating can empower the clock signals from the Clock Distribution Network (CDN). This system could be initiating the clock which is required for the activity of the circuit.

The superfluous clock signals are not enacted during the clock gating. This spares the dynamic power of the circuit. The auto gated flip flops which are to utilize clock gating system for just little power utilization. The tale approach is a circuit configuration dependent on look forward clock gating which is to be utilized for the planning requirements for each clock beats. The empowering clock beats for the inferred timing sign to the gated rationale which is to be spares the power from the flipflops.

Example:-

$$Y_{L} = \begin{bmatrix} h_{0} & h_{1} & h_{2} & h_{3} & h_{4} \end{bmatrix} \begin{bmatrix} m_{1} \\ m_{2} \\ m_{3} \\ m_{4} \\ m_{5} \end{bmatrix}$$

Where

m1 = X(n) + X(n-8) $m^2 = X(n-1) + X(n-7)$ m3 = X(n-2) + X(n-6)m4 = X(n-3) + X(n-5)m5 = X(n-4)

Putting the value of h(0), h(1), h(2), h(3), h(4) and m1, m2, m3, m4, m5 from the above equation

$$Y_{H} = \begin{bmatrix} 77 & 34 & -10 & -2 & 3 \end{bmatrix} \bullet \begin{bmatrix} 2 \\ 2 \\ 2 \\ 2 \\ 1 \end{bmatrix} = 201$$

Step-1: All of the input converts' binary number

$m_1 = 010, m_2 = 010, m_3 = 010, m_4 = 010, m_5 = 001$ Step-2: All of the binary enter carried out to sign extension so, s(1) = 0010, s(2) = 0010, s(3) = 0010, s(4) = 0010, s(5) = 0001

Step-3: All of the sign extensions enter carried out to adder array so,

$$m(1) = 0011 , m(2) = 0111 , m(3) = 0110 ,$$

$$m(4) = 0100, m(5) = 0100,$$

$$m(6) = 0110 , m(7) = 0110$$

$$m(8) = not(m_3 + m_4) + 1 = 1100$$

Step-4: The entire adder array enters applied to MUX so, the whole adder array enter proper shift 1-bit so MUX (1) =  $0'0011 = Y_p(0)$

MUX (1) add MUX (2) =  $Y_P(1)$

= 0'0011+ 0.111= 10001Output of the  $Y_P(1)$  again right shift 1-bit and adds MUX (3) so = 0'10001+ 0110= 101001Output of the  $Y_P(2)$  again right shift 1-bit and adds MUX (4) so = 0'101001+ 0.100= 1.001001Output of the  $Y_P(3)$  again right shift 1-bit and adds MUX (5) so = 0'1001001+ 0.100 $= 1\,0001001$ Output of the  $Y_P(4)$  again right shift 1-bit and adds MUX (6) so = 0'10001001+ 0.110= 101001001Output of the  $Y_P(5)$  again right shift 1-bit and adds MUX (7) so = 0'101001001+ 0.110= 1011001001Output of the  $Y_P$  (6) again right shift 1-bit and adds MUX (8) so = 0'1011001001+ 1100**Final output** = 0.0011001001201

$Y_{P}(6)$

=

# ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE)

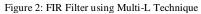

#### **BRENT KUNG ADDER**

BKA is logical gate and consists of XOR\_gate, OR\_gate and AND\_gate. These types of adder are followed by chain rules and get output of BKA. It acquainted normality with the design of the adder and has less wiring issues, reduces complexities and provides better execution and less chip region.

#### V. RESULT AND SIMULATION

Figure 4 and Figure 5 are shows the RTL view and VHDL test waveform of multiplier less distributive arithmetic based FIR filter. Proposed algorithm and previous algorithm are shows result in Table I to Table III. The proposed algorithm is efficient delay and slice in previous algorithm. Table I shows the result of the advance HDL synthesis report and Table II shows the result of the synthesis device family.

| A 1 .            |          | V   |

|------------------|----------|-----|

| Architecture     | Register | Xor |

| Multiplier based | 32       | 432 |

| FIR              | -        | -   |

| III              |          |     |

| Multiplier less  | 12       | 356 |

| FIR Filter       |          |     |

|                  |          |     |

| Architecture    | Slice     | LUTs | FF Pairs |

|-----------------|-----------|------|----------|

|                 | Registers |      |          |

| Multiplier      | 37        | 186  | 34       |

| based FIR       |           |      |          |

| Multiplier less | 27        | 141  | 19       |

| FIR Filter      |           |      |          |

Table II: Synthesis Device Report

#### Table III: Timing Summary

| Architecture    | Minimum    | Maximum     |

|-----------------|------------|-------------|

|                 | Period     | Frequency   |

| Multiplier      | 4.654 nsec | 419.643 MHz |

| based FIR       |            |             |

| Multiplier less | 1.598 nsec | 625.821 MHz |

| FIR Filter      |            |             |

# VI. CONCLUSION

From the investigation it's found that the proposed technique expends less area when contrasted with the customary technique. The area utilization of the cradle stages are decreased in the proposed technique. The execution is completed in 60nm and 90nm innovation. The 60nm innovation gives better outcomes when contrasted with higher innovation. Circuit recreation showed that the proposed design uses the common part engineering through which number of parts is decreased. The sequencing of information is appropriately gated. The clock gating is effective and the altered mirror flip-flop engineering decreases the blunder in the framework. The hub voltage stays in full rail to rail swing despite the fact that the engineering isn't proposed to drive loads. When looked at with existing techniques the effectiveness of proposed strategy is improved and discovered that the power utilization is diminished maximally.

#### REFERENCES

- Ranendra Kumar Sarma et al.; A NOVEL TIME-SHARED AND LUT-LESS PIPELINED ARCHITECTURE FOR LMS ADAPTIVE FILTER; IEEE Transactions on VLSI Systems; pp. 01-10. IEEE, 2019.

- [2] Anubhuti Mittal et al.; COMPARATIVE STUDY OF 16-ORDER FIR FILTER DESIGN USING DIFFERENT MULTIPLICATION TECHNIQUES; IET Circuits Devices Syst., Vol. 11. No 3. pp. 196-200. IET, 2017.

- [3] Vijaya Lakshmi Bandi et al.; PERFORMANCE ANALYSIS FOR VEDIC MULTIPLIER USING MODIFIED FULL ADDERS; International Conference on Innovations in Power and Advanced Computing Technologies, IEEE, 2017.

- [4] Basant Kumar Mohanty et al.; HIGH PERFORMANCE FIR FILTER ARCHITECTURE FOR FIXED AND RECONFIGURABLE APPLICATIONS; IEEE TRANSACTIONS ON VLSI SYSTEMS, Vol. 78. No.06. IEEE, 2016.

- [5] K. Deergha Rao et al.; FPGA IMPLEMENTATION OF COMPLEX MULTIPLIER USING MINIMUM DELAY VEDIC REAL MULTIPLIER ARCHITECTURE; International Conference on Electrical, Computer and Electronics Engineering, IEEE, 2016.

- [6] K. Deergha Rao et al.; FPGA IMPLEMENTATION OF COMPLEX MULTIPLIER USING MINIMUM DELAY VEDIC REAL MULTIPLIER ARCHITECTURE; International Conference on Electrical, Computer and Electronics Engineering, IEEE, 2016.

- [7] Indranil Hatai et al.; AN EFFICIENT VLSI ARCHITECTURE OF A RECONFIGURABLE PULSE-SHAPING FIR INTERPOLATION FILTER FOR MULTI-STANDARD DUC; IEEE Transactions on VLSI Systems, Vol. 23. No. 6. IEEE, 2015.

- [8] Sang Yoon Park et al.; EFFICIENT FPGA AND ASIC REALIZATIONS OF DA-BASED RECONFIGURABLE FIR DIGITAL FILTER; IEEE Transactions on Circuits and Systems-II, IEEE, 2014.

- [9] B. K. Mohanty et al.; MEMORY FOOTPRINT REDUCTION FOR POWER-EFFICIENT REALIZATION OF 2-D FINITE IMPULSE RESPONSE FILTERS; IEEE Trans. Circuits Syst. I, Vol. 61. No. 1. pp. 120–133, IEEE, 2014.

- [10] Madhu Thakur et al.; Design of Braun Multiplier with Kogge-Stone Adder & It's Implementation on FPGA; International Journal of Scientific & Engineering Research, Vol. 3. No. 10. pp. 03-06. IEEE 2012.