IJRECE VOL. 7 ISSUE 2 (APRIL- JUNE 2019)

# Study of Shift Registers, Storage Capacities and its Classifications

Ekta, Msc. Physics

Abstract- This sequential device loads the data present on its inputs and then moves or "shifts" it to its output once every clock cycle, hence the name Shift Register.

A shift register basically consists of several single bit "D-Type Data Latches", one for each data bit, either a logic "0" or a "1", connected together in a serial type daisy-chain arrangement so that the output from one data latch becomes the input of the next latch and so on. Data bits may be fed in or out of a shift register serially, that is one after the other from either the left or the right direction, or all together at the same time in a parallel configuration.

The number of individual data latches required to make up a single Shift Register device is usually determined by the number of bits to be stored with the most common being 8-bits (one byte) wide constructed from eight individual data latches.

Shift Registers are used for data storage or for the movement of data and are therefore commonly used inside calculators or computers to store data such as two binary numbers before they are added together, or to convert the data from either a serial to parallel or parallel to serial format. The individual data latches that make up a single shift register are all driven by a common clock (Clk) signal making them synchronous devices.

Key Words- Shift Register, Flip- Flops, Counter etc.

## **Counter:**

A register that goes through a predetermined sequence of states Classification

The shift registers can be classified as

- Serial In Serial Out(SISO) Shift Registers

- Serial In Parallel Out (SIPO)Shift Registers

- Parallel In Serial Out (PISO)Shift Registers

- Parallel In Parallel Out (PIPO)Shift Registers

## Serial In - Serial Out Shift Registers

The serial in/serial out shift register accepts data serially - that is, one bit at a time on a single line. It produces the stored information on its output also in serial form.

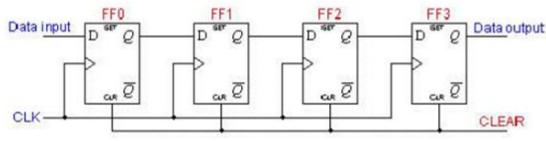

Basic four-bit shift register

A basic four-bit shift register can be constructed using four D flip-flops, as shown in Fig

The operation of the circuit is as follows.

- The register is first cleared, forcing all four outputs to zero.

- The input data is then applied sequentially to the D input of the first flip-flop on the left (FF0).

- During each clock pulse, one bit is transmitted from left to right.

- Assume a data word to be 1001.

- The least significant bit of the data has to be shifted through the register from FF0 to FF3.

Fig.1: Basic Four bit shift register

In order to get the data out of the register, they must be shifted out serially. The data is loaded to the register when the control line is HIGH (i.e. WRITE). The data can be shifted out of the register when the control line is LOW (i.e. READ). Fig. 2.2 illustrates entry of the four bits 1010 into the register.

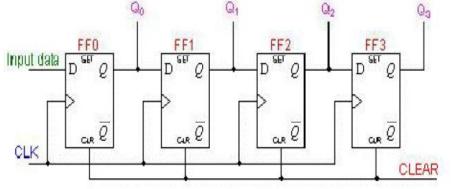

### Serial In - Parallel Out Shift Registers

For this kind of register, data bits are entered serially in the same manner as discussed in the last section. The difference is the way in which the data bits are taken out of the register. Once the data are stored, each bit appears on its respective output line, and all bits are available simultaneously. A construction of a four-bit serial in - parallel out register is shown below.

Fig.2: A four-bit serial in - parallel out register

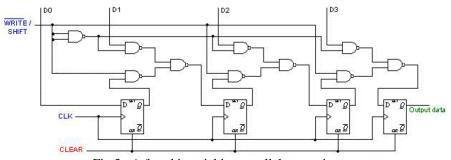

D0, D1, D2 and D3 are the parallel inputs, where D0 is the most significant bit and D3 is the least significant bit. To write data in, the mode control line is taken to LOW and the data is clocked in. The data can be shifted when the mode control line is HIGH as SHIFT is active high

#### Parallel In - Serial Out Shift Registers

A four-bit parallel in - serial out shift register is shown below. The circuit uses D flip-flops and NAND gates for entering data (i.e. writing) to the register.

Fig.3: A four-bit serial in - parallel out register

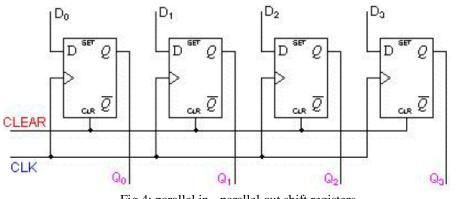

## Parallel In - Parallel Out Shift Registers

For parallel in - parallel out shift registers, all data bits appear on the parallel outputs immediately following the simultaneous entry of the data bits. The following circuit is a four-bit parallel in - parallel out shift register constructed by D flip-flops.

Fig.4: parallel in - parallel out shift registers

The D's are the parallel inputs and the Q's are the parallel outputs. Once the register is clocked, all the data at the D inputs appear at the corresponding Q outputs simultaneously.

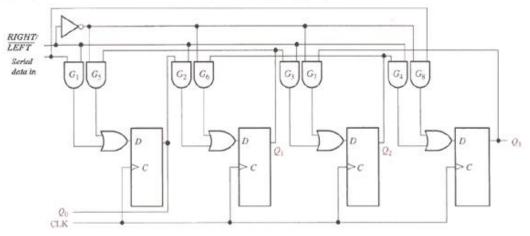

#### **Bidirectional Shift Registers**

The registers discussed so far involved only right shift operations. Each right shift operation has the effect of successively dividing the binary number by two. If the operation is reversed (left shift), this has the effect of multiplying the number by two. With suitable gating arrangement a serial shift register can perform both operations. A bidirectional, or reversible, shift register is one in which the data can be shift either left or right. A four-bit bidirectional shift register using D flip-flops is shown below.

Fig.5: Bi Directional Shift Register

#### Storage Capacity:

The storage capacity of a register is the total number of bits (1 or 0) of digital data it can retain. Each stage (flip flop) in a shift register represents one bit of storage capacity. Therefore the number of stages in a register determines its storage capacity.

#### **References :**

- [1]. https://www.electronics-tutorials.ws/sequential/seq\_5.html

- [2]. https://circuitdigest.com/tutorial/what-is-shift-register-types-applications

- [3]. https://www.tutorialspoint.com/digital\_circuits/digital\_circuits\_shift\_registers

- [4]. https://www.daenotes.com/electronics/digital-electronics/shift-registers