# DESIGN AND PROPOSE THE HIGH SPEED LFSR CIRCUIT USING SST METHOD

# KARTHIK MALLAPPAHALLI SHEKARAPPA<sup>1</sup>, HEMACHANDRA REDDY K<sup>2</sup>

<sup>1</sup>Btech student, Dept of EEE, Global Academy of Technology, RR Nagar, Bengaluru, Karnataka-560098, India <sup>2</sup>Associate professor, Dept of EEE, Global Academy of Technology, RR Nagar, Bengaluru, Karnataka-560098, India

Abstract - Straight comments change register is a vital part of the cyclic redundancy check (CRC) procedures and also BCH encoders. This thesis offers a mathematical evidence of presence of a direct improvement to change LFSR circuit's right into equal state room solutions. This makeover accomplishes a complete speed-up contrasted to the serial style at the expense of a rise in equipment expenses. This technique relates to all irreducible polynomials made use of in CRC procedures and also BCH encoders. A brand-new solution is suggested to change the LFSR right into the type of a CRC filter. We recommend a unique broadband parallel LFSR style based upon identical Infinite Impulse Response (CRC) filter style, pipelining and also retiming formulas. The benefit of recommended technique over the previous designs is that it has both feed onward and also responses courses. We additionally suggest using consolidated parallel as well as pipelining methods to remove the fan-out impact in lengthy generator polynomials. The suggested system can be put on any kind of generator polynomial, i.e., any kind of LFSR as a whole. A contrast in between the recommended as well as previous designs reveals that the suggested parallel design attains the very same essential course as that of previous styles with a minimized equipment price.

# I. INTRODUCTION

Interaction criteria remain to be specified that press bench greater for throughput. For instance, 10 Gbps IEEE 802.3 ak was standard in 2003, and also lately 100 Gbps IEEE 802.3 bachelor's degree is standard in 2010. In order to sustain these high throughput needs at a sensible regularity, identical designs are needed. At the very same time, the power intake as well as equipment expenses must be maintained to a minimum. The study in this thesis is guided in the direction of developing high throughput designs for 2 crucial elements of the modern-day interaction criteria, CRC/BCH encoders as well as Fast Fourier Transform (FFT). Cyclic Redundancy Check (CRC) is commonly utilized in information interactions as well as storage space tools as a reliable method to discover transmission mistakes. Instances of data criteria that utilize CRC consist of Asynchronous Transfer Mode (ATM), Ethernet (IEEE 802.3), WiFi (IEEE 802.11) as well as WiMAX (802.16). The Bose-Chaudhuri Hochquenghem

(BCH) codes are just one of one of the most effective algebraic codes as well as are thoroughly made use of in modern-day interaction systems. Contrasted to Reed-Solomon codes, BCH codes can attain around added 0.6 dB coding gain over the additive white Gaussian sound (AWGN) network with comparable price and also codeword size. Numerous applications of BCH codes such as long-haul optical interaction systems made use of in International Telecommunication Union-Telecommunication Standardization market (ITU-T) G. 975, magnetic recording systems, solid-state storage space gadgets and also data call for high throughput along with huge mistake remedying capacity. Thus, BCH codes are of wonderful passion for their reliable as well as broadband equipment inscribing and also translating 1 2 execution. The BCH encoders and also CRC procedures are traditionally executed by a direct responses change register (LFSR) style. While such a design is straightforward as well as can perform at high regularity, it deals with serial-in as well as serial-out restriction. In optical interaction systems, where throughput over 1 Gbps is generally wanted, the clock regularity of such LFSR based encoders cannot stay up to date with information transmission price and also therefore identical handling should be used. Increasing the information size, i.e 2 identical designs does not increase the throughput, the most awful instance timing course comes to be slower. Because the identical designs consist of responses loopholes, pipelining cannot be put on decrease the important course. An additional concern with the identical designs is equipment intricacy.

#### LITERATURE SURVEY

II.

In order to fulfill the enhancing need on handling capacities, much study has actually been accomplished on identical styles of LFSR for CRC as well as BCH encoders. In [5], very first serial to parallel change of direct responses change register was defined as well as was initial related to CRC calculation. A number of various other methods have actually been 6 just recently offered to parallelize LFSR calculations. A unique parallel CRC style based upon state area depiction is recommended in the literary works. The primary benefit of this style is that the intricacy is changed out of the comments loophole. The complete speedup can be attained by pipelining

the feedforward courses. A state area improvement has actually been suggested to decrease intricacy yet the presence of such an improvement was not confirmed and also whether such a makeover is special has actually been unidentified thus far. In this thesis, we offer a mathematical evidence to reveal that such a change exists for all CRC and also BCH generator polynomials. We likewise reveal that this makeover is nonunique. As a matter of fact, we reveal the presence of boundless such improvements and also exactly how these can be obtained. We after that suggest unique systems based upon pipelining, retiming and also look in advance calculations to lower the important course in the identical styles based upon parallel as well as pipelined CRC filter style.

#### III. BASIC LINEAR FEEDBACK SHIFT REGISTERS

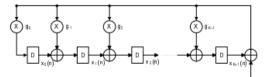

CRC calculations as well as BCH encoders are applied by utilizing Linear Feedback Shift Registers [1] a consecutive LFSR circuit cannot fulfill the rate needed when high-speed information transmission is called for. Due to this restriction, identical designs need to be used in high-speed applications such as optical interaction systems where the throughput of a number of gigabits/sec is called for. LFSRs are likewise made use of in standard Design for Test (DFT) and also Built-in Self Test (BIST) [4] LFSRs are made use of to perform action compression in BIST, while for the DFT, it provides pseudorandom binary examination series. A fundamental LFSR style for Kth order creating polynomial in GF(2) is received Fig. 2.1. K represents the size of the LFSR, i.e., the variety of hold-up components and also g0, g1, g2, ..., gK stand for the coefficients of the particular polynomial. The particular polynomial of this LFSR is

$$g(x) = g0 + g1x + g2x 2 + ... + gKx K$$

#### Fig. 3.1.Basic LFSR architecture.

Where g0, g1, g2, ..., gK  $\in$  GF(2). Normally, gK = g0 = 1. In GF(2), multiplier aspects are either open circuits or brief circuits i.e., gi = 1 suggests that a link exists. On the various other hand gi = 0 indicates that no link exists as well as the matching XOR gateway can be changed by a straight line from input to result. Allow u(x), for x = 0, 1, ... N - 1, u(x)  $\in$ GF(2),  $0 \le n \le N - 1$  be input series of size N. Both CRC calculation as well as BCH encoding entail the department of the polynomial u(x)x K by g(x) to get the rest, Rem(u(x)x K)g(x). Throughout the very first N clock cycles, the N-bit

message is input to the LFSR with the majority of considerable little bit (MSB) initially. At the exact same time, the message little bits are likewise sent out to the result to develop the BCH inscribed codeword. After N clock cycles, the comments is reset to absolutely no as well as the K signs up have the coefficients of Rem(u(x)x K)g(x). In BCH inscribing, the continuing to be little bits are after that changed out little by little to develop the staying methodical codeword little bits. The throughput of the system is restricted by the breeding hold-up around the responses loophole, which includes 2 XOR gateways. We can boost the throughput by changing the system to refine some variety of little bits in parallel.

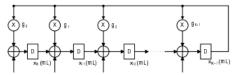

#### IV. PROPOSED METHOD 4.1 STATE SPACE REPRESENTATION OF LFSR

An identical LFSR style based upon state room calculation has actually been recommended. The LFSR displayed in Fig. 1 can be explained by the formula x(n + 1) = Ax(n) + bu(n);  $n \ge 0$ . With the preliminary state x(0) = xo. The Kdimensional state vector x(n) is provided by x(n) = [x0(n) x1(n) ... xK - 1(n)] T and also A is the K × K matrix provided by

$$\mathbf{A} = \begin{bmatrix} 0 & 0 & 0 & \dots & 0 & g_0 \\ 1 & 0 & 0 & \dots & 0 & g_1 \\ 0 & 1 & 0 & \dots & 0 & g_2 \\ \dots & \dots & \dots & \dots & \dots \\ 0 & 0 & 0 & \dots & 1 & g_{K-1} \end{bmatrix}$$

The K × 1 matrix b is b = [g0 g1 ... gK - 1] T. The result of the system is the rest of the polynomial department that it calculates, which the state vector itself is. We call the outcome vector y(n) and also include the outcome formula y(n) = Cx(n) to the state formula with C equivalent to the K × K identification matrix. The coefficients of the generator polynomial g(x) show up in the right-hand column of the matrix A. Note that, this is the buddy matrix of polynomial g(x) and also g(x) is the particular polynomial of this matrix. The first state xo depends upon the details interpretation of the CRC for a provided application.

#### **4.2 STATE SPACE TRANSFORMATION**

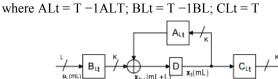

A straight change has actually been recommended to lower the intricacy in the comments loophole. The state area formula of L-parallel system with a specific outcome formula is referred to as

x(mL + L) = ALx(mL) + BLuL(mL); y(mL) = CLx(mL)Where CL = I, the K × K identification matrix. The result vector y(mL) amounts to the state vector which has the rest at m = N/L. Think about the straight change of the state vector x( mL) with a consistent non-singular matrix T, i.e., x(mL) = Txt(mL). Offered T as well as its inverted, we can reveal the state area formula (2.5) in regards to the state vector xt(mL),

as adheres to: xt( mL + L) = ALtxt( mL) + BLtuL( mL); y( mL) = CLtxt( mL).

Fig.4.1.Changed LFSR Architecture utilizing state room

Fig.4.2. Modified feedback loop of Fig. 2

And also T is the makeover matrix. The identical LFSR style after the change is displayed in Fig as well as the customized responses loophole. We can observe from the number that if ALt is a buddy matrix, after that the intricacy of the responses loophole will certainly be like that of the initial LFSR. If there exists a T such that ALt is a friend matrix, after that the intricacy in the responses loophole boils down. It appears that (2.6) stands for a resemblance change and also we can specify that there exists a T such that ALt is a friend matrix if and also just if AL resembles buddy matrix. The adhering to thesis shows that AL resembles a friend matrix gave the generator polynomial is irreducible. The last problem is satisfied for all CRC as well as BCH codes.

#### V. SIMULATION RESULTS

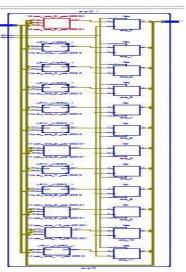

| Device Utilization Summary (estimated values) |      |           | E           |

|-----------------------------------------------|------|-----------|-------------|

| Logic Utilization                             | Used | Available | Utilization |

| Number of Slices                              | 7    | 4656      | 0%          |

| Number of Slice Flip Flops                    | 12   | 9312      | 0%          |

| Number of 4 input LUTs                        | 12   | 9312      | 0%          |

| Number of bonded IOBs                         | 26   | 232       | 11%         |

| Number of GCLKs                               | 1    | 24        | 4%          |

Fig.5.1.Design Summary

Fig.5.2.Rtl schematic

Fig.5.4. Time delay

## VI. CONCLUSION

This paper has actually offered a total mathematical evidence to reveal that a change exists in state area to lower the intricacy of the identical LFSR responses loophole. This brings about an unique approach for broadband parallel execution of direct responses change signs up which is based

upon identical CRC filter style. Our style can lower the important course without enhancing the equipment price at the very same time. The layout applies to any kind of sort of LFSR style. Additionally we reveal that making use of consolidated pipelining as well as parallel handling strategies of CRC filtering system, vital course in the responses component of the style can be minimized. The big fan-out result trouble can likewise be reduced with some equipment expenses by retiming around those specific nodes.

## VII. REFERENCES

- [1]. T. V. Ramabadran in addition to S.S. Gaitonde, "A Tutorial on CRC Computations," IEEE Micro., Aug. 1988.

- [2]. R. E. Blahut, Theory as well as likewise Practice of Error Control Codes. Looking into, MA: Addison Wesley, 1984

- [3]. W. W. Peterson along with D. T. Brown, "Cyclic codes for errot exploration", Proc. RAGE, vol.49, pp. 228-235, Jan. 1961.

- [4]. N. Oh, R. Kapur, T. W. Williams, "Fast seed estimation for reseeding adjustment register in assessment pattern compression," IEEE ICCAD, 2002, pp. 76-81.

- [5]. M. Y. Hsiao as well as additionally K. Y. Sih, "Serial-to-parallel remodeling of straight actions alter register circuits", IEEE Trans. Digital Computers, vol. EC-13, pp. 738-740, Dec. 1964.