## VLSI ARCHITECTURE OF FLEXIBLE MACROBLOCK ORDERING/MANCHESTER ENCODING WITH SOLS METHOD K.MANASA<sup>1</sup>, Dr. J. NARENDRA BABU<sup>2</sup>

<sup>1</sup>P.G Student, Department of Electronics and Communication Engineering

2 Professor, Department of Electronics and Communication Engineering, Siddhartha Institute Of

Engineering And Technology.

(E-mail: manasa1205@gmail.com)

Abstract— Encoding strategies are getting important part in communication. Strategies like Manchester, and FM0 encoding are utilized as a part of various applications. Every strategy has distinctive activities relies upon their requirements. Every single encoding plans are utilized without losing any of its parameters. This paper receives similarity oriented logic simplification technique (SOLS) which combines design and synchronize the task and furthermore DSRC system is utilized to keep up the dc balance and signal reliability. By applying both the procedures we can diminish the number of transistors and keeps up the DC adjust. The present work manages getting an incorporated design of FMO, Manchester encoding to conquer a few disadvantages of traditional method. In this presented approach the number of hardware components is lessened, subsequently brings about the decrease of overall area consumed by the additional usefulness in Dedicated Short Range Communication (DSRC).

**Keywords**—component; formatting; style; styling; insert (key words)

## I. Introduction

Encoding utilized for communication to change over the data in to reasonable form for transmission. Encoding strategies can likewise be utilized for security purposes. This kind of encoding is used at the transistor level, so it can be utilized with optical communication. FMO, Manchester and mill operator coding methods are utilized as a part of this paper to encode the information while transmit the flag through UART medium. Since encoding assumes the dynamic part in secured communication, creating engineering for such encoding procedures utilizing SOLS technique by DSRC application. DSRC is a protocol for maybe a couple way medium range communication particularly for canny transportation frameworks. Empowers the message sending and broadcasting among automobiles for security issues and open data declaration and particularly valuable in the ETC -Electronic Toll Collection framework. If there should arise an occurrence of ETC framework, the toll gathering is electrically proficient with the IC-card stages that are contactless. The SOLS can be actualized with two strategies specifically adjust logic sharing and territory conservative retiming. The zone minimal retiming used to decrease the transistor checks and adjust logic activity sharing is utilized on the transistor level, so it can be utilized with to consolidate the FM0 and Manchester encoding plans.

## II. LITERATURE REVIEW

Yu-hsuan lee and cheng-weipan (2014) examined about the coding-decent variety among the FM0 and Manchester codes truly constraining the outline of the completely reused VLSI engineering for both the encoding plans. In this paper, the similarity oriented logic simplification (SOLS) strategy is presented to beat this restriction. John B. Kenney (2011) done the investigation on automotive industry, The business is in the skirt of creating devoted short- range communication hardware, for use in vehicle to vehicle and vehicle to street side correspondence. Depends of the helpful standards for interoperability chooses the adequacy of this innovation. Yu-Cherng Hung, Min-Ming Kuo, et al., (2009) presented an adjusted Manchester encoder that can work in high frequency with simple circuit structure. The idea has embraced the idea of parallel task was utilized to ad lib the information throughput. Here notwithstanding that, this strategy of equipment sharing is received in the presented configuration to decrease the number of transistors. Accordingly, P. Benabes, A. Gauthier, and J. Ohman, (2003) depicted another Manchester code generator which is planned at the transistor level. The generator depicted utilizations 32 transistors and has an indistinguishable unpredictability from a standard D flip-tumble. The primary preferred standpoint of this outline is utilizing a clock flag which is having the comparative recurrence as the information. Yield minor departure from the rising edge and falling edge of the clock. Ayoub Khan, Manoj Sharma, et al, (2008) offered an abnormal state engineering of label emulator and endeavored to show a high concentration to utilize the RFID Emulator as information transport gadget and level outline of UHFRFID label emulator and execution settling instrument. amalgamation result exhibits that FSM configuration is of FM0 encoders to be utilized as a part of the RFID label proficient and we have accomplished working frequency of emulator 192.641 MHz and 188.644MHz for FM0 encoders.

## III. PROPOSED WORK

## A. FM0/Manchester encoder:

The reason for SOLS method is to outline a completely reused VLSI design for FM0, Manchester encodings. The SOLS method is ordered into two sections Area-compact retiming and Balance logic-operation sharing. The area-compact retiming moves the hardware to less number of transistors. The adjust logic-operation joins distinctive encodings with the indistinguishable logic parts to accomplish

the DC with the indistinguishable logic segments to accomplish the DC balance and flag signal reliability.

## Area compact retiming

For fm0 the state code of the each state is put away into DFFA and DFFB .the change of the state code is just relies upon the past province of B(t-1) rather than the both A(t-1) and B(t-1). The past state is signified as the A(t-1) and after that the B(t-1) and then the present state is meant as the A(t) and after that the B(t).

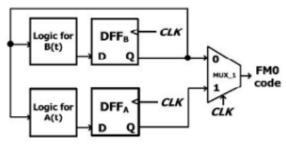

Fig 1: Without area compact retiming

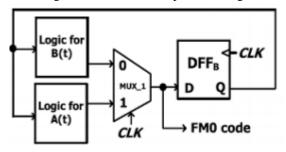

Fig 2: With area compact retiming

Thus, the FM0 encoding just requires a single 1-bitflip- flop to store the past esteem B(t-1).If the DFF<sub>A</sub> is straightforwardly expelled, a non synchronization amongst A(t) and B(t)causes the logic blame of FM0 code. To maintain a strategic distance from this logic blame, the DFF<sub>B</sub> is migrated directly after the MUX-1, where the DFF<sub>B</sub> is expected be positive edge activated flip flop. At each cycle, the FM0 code, including An and B, is gotten from the logic of A(t) and the logic of B(t), individually.

The FM0 code is then again traded among A(t) and B(t) through the MUX-1 by the control banner of the CLK. In the Q of DFFB is clearly invigorated from the rationale of B(t)with 1-cycle idleness. right when the CLK is rationale 0, the B(t) is experienced MUX-1 to the D of DFFB. By then, the best in class positive-edge of CLK invigorates it to the Q of DFFB. the arranging graph for the Q of DFFB is dependable whether the DFFB is moved or not.

the B(t) is gone through MUX-1 to the D of DFFB. At that point, the upcoming positive-edge of CLK refreshes it to the Q of DFFB. The planning outline for the Q of DFFB is steady whether the DFFB is migrated or not. The transistor check of the FM0 encoding design without territory minimized retiming is 72, and that with region reduced retiming is 50. The zone conservative retiming method decreases 22 transistors.

## **Balance logic operation sharing:**

The Manchester encoding is determined utilizing the XOR activity. the condition of the XOR gate is given underneath. X ⊕CLK=X CLK+~ X CLK

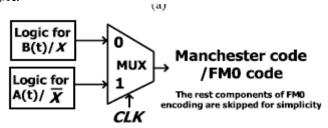

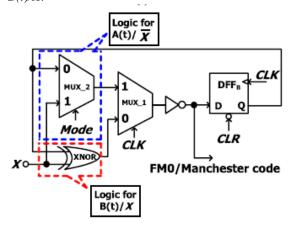

the idea of adjust logic-operation sharing is to incorporate the X into A(t) and X into B(t).the fm0 and Manchester logic s have a typical purpose of the multiplexer like logic with the choice of the CLK. the chart for the adjust logic activity sharing given the accompanying.

The A(t) can be gotten from an inverter of B(t -1), and X is acquired by an inverter of X. The logic for A(t)/X can have a similar inverter, and afterward a multiplexer is put before the inverter to switch he operands of B(t -1) and X. The Mode shows eitherFM0 or Manchester encoding is received. The comparable idea can be likewise connected to the logic for B(t)/X.

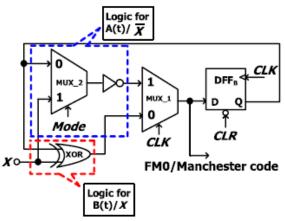

Fig 3: Balance logic operation sharing

By the by, this engineering shows a disadvantage that the XOR is devoted for FM0 encoding, and isn't imparted to Manchester encoding. Accordingly, the HUR of this design is absolutely restricted. The X can be likewise deciphered as the X 0, and in this way the XOR activity can be imparted to Manchester and FMO encodings, where the multiplexer unreliable to switch the operands of B(t-1) and logic 0. This engineering shares the XOR for both B(t) and X, and there by expands the HUR. At the point when the FM0 code is embraced, the CLR is incapacitated, and the B(t-1) can be gotten from DFFB .Hence, the multiplexer can be completely spared, and its capacity can be totally incorporated into the migrated DFF. The logic for A(t)/X incorporates the MUX-2 and an inverter. Rather, the logic for B(t)/X just fuses a XOR door. In the logic for A(t)/X, the calculation time of MUX-2is relatively indistinguishable to that of XOR in the logic for B(t)/X. Be that as it may, the logic for A(t)/Xadditionally joins an inverter in the arrangement of MUX-2. This unbalance calculation time between A(t)/X and B(t)/X brings about the glitch to MUX-1, possibly causing the logic blame on coding. To mitigate this unbalance calculation time, the design of the adjust calculation time between A(t)/X and B(t)/X The XOR in the logic for B(t)/X is converted into the XNOR with an inverter, and after that this inverter is imparted to that of the logic for A(t)/X. This mutual inverter is migrated in reverse to the yield of MUX-1. Along these lines, the logic calculation time between A(t)/X and B(t)/X is more adjust to each other.

# B VLSI architecture of FM0 and Manchester encodings using SOLS

FM0 code : Mode = 0 and CLR = 1 Manchester code : Mode = 1 and CLR = 0

Fig 4: Unbalance computation time between A(t)/X and B(t)/X.

FM0 code : Mode = 0 and CLR = 1 Manchester code : Mode = 1 and CLR = 0

Fig 5: Equalization calculation time between A(t)/X and B(t)/X.

The presented VLSI architecture of FM0/Manchester encoding utilizing SOLS strategy is appeared in Fig. 4. The Logic for A(t)/X incorporates the MUX-2 and an inverter. Rather, the logic for B(t)/X just consolidates a XOR entryway. In the logic for A(t)/X, the calculation time of MUX-2 is relatively indistinguishable to that of XOR in the logic for B(t)/X. Be that as it may, the logic for A(t)/X additionally consolidates an inverter in the arrangement of MUX-2. This unbalance calculation time between A(t)/X and B(t)/X brings about the glitch to MUX-1, conceivably causing the logic blame on coding. To mitigate this unbalance calculation time, the design of the adjust calculation time between A(t)/X and B(t)/X is appeared in Fig.5.

The XOR in the logic for B(t)/X is converted into the XNOR with an inverter, and after that this inverter is imparted to that of the logic for A(t)/X. This mutual inverter is migrated in

reverse to the yield of MUX-1. Along these lines, the logic calculation time between A(t)/X and B(t)/X is more adjust to each other. The selection of FM0 or Manchester code relies upon Mode and CLR. Also, the CLR additionally has another individual capacity of an equipment instatement.

On the off chance that the CLR is basically inferred by transforming Mode without allotting an individual CLR control flag, this prompts a contention between the coding mode choice and the equipment instatement. To stay away from this contention, both Mode and CLR are thought to be independently distributed to this plan from a framework controller.

Regardless of whether FM0 or Manchester code is received, no logic component of the presented VLSI design is squandered. Each part is dynamic in both FM0 and Manchester encodings. In this way, the HUR of the presented VLSI engineering is significantly moved forward.

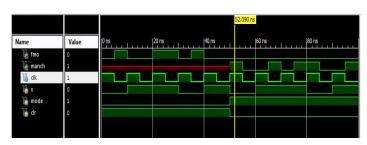

### IV.SIMULATION RESULTS

Fig 6.simulation waveforms

| )ffset:                       | 6.769ns (Levels of Logic = 2) |                  |                |                         |  |  |  |  |  |  |

|-------------------------------|-------------------------------|------------------|----------------|-------------------------|--|--|--|--|--|--|

| Source:                       | C1/out 7 (FF)                 |                  |                |                         |  |  |  |  |  |  |

| Destination:                  | out<8> (PAD)                  |                  |                |                         |  |  |  |  |  |  |

| Source Clock:                 |                               | clk out rising   |                |                         |  |  |  |  |  |  |

| Data Path: C1/ou              | _<br>t_7 to out<8>            | Sate             | Net            |                         |  |  |  |  |  |  |

|                               | _<br>t_7 to out<8>            | Sate             | 173.7373       | Logical Name (Net Name) |  |  |  |  |  |  |

| Data Path: C1/ou              | t_7 to out<8>  fanout De      | Sate             | Delay          | Logical Name (Net Name) |  |  |  |  |  |  |

| Data Path: C1/ou Cell:in->out | t_7 to out<8>  fanout De      | Sate<br>elay<br> | Delay<br>0.590 |                         |  |  |  |  |  |  |

Fig 7.Delay Report

| On-Chip Power Summary |           |   |            |   |      |   |           |   |             |     |      |

|-----------------------|-----------|---|------------|---|------|---|-----------|---|-------------|-----|------|

| ı                     | On-Chip   | 1 | Power (mW) | 1 | Used | 1 | Available | 1 | Utilization | (%) | 0000 |

|                       | Clocks    | 1 | 1.30       | 1 | 3    | 1 | (0.000)   | 1 | (0.00.03)   |     | 95   |

| ĺ                     | Logic     | 1 | 0.00       | 1 | 10   | 1 | 11776     | 1 |             | 0   |      |

| ĺ                     | Signals   | 1 | 0.00       | 1 | 20   | 1 |           | 1 | (2000)      |     |      |

| ĺ                     | IOs       | 1 | 0.00       | 1 | 20   | 1 | 372       | 1 |             | 5   |      |

| ı                     | Quiescent | 1 | 31.52      | 1 |      | 1 |           | 1 |             |     |      |

| ĺ                     | Total     | 1 | 32.83      | 1 |      | 1 |           | 1 |             |     |      |

Fig 8.Power Report

| Device Utilization Summary                     |      |           |             |         |  |  |  |

|------------------------------------------------|------|-----------|-------------|---------|--|--|--|

| Logic Utilization                              | Used | Available | Utilization | Note(s) |  |  |  |

| Number of Slice Flip Flops                     | 10   | 11,776    | 1%          |         |  |  |  |

| Number of 4 input LUTs                         | 10   | 11,776    | 1%          |         |  |  |  |

| Number of occupied Slices                      | 9    | 5,888     | 1%          |         |  |  |  |

| Number of Slices containing only related logic | 9    | 9         | 100%        |         |  |  |  |

| Number of Slices containing unrelated logic    | 0    | 9         | 0%          |         |  |  |  |

| Total Number of 4 input LUTs                   | 12   | 11,776    | 1%          |         |  |  |  |

| Number used as logic                           | 10   |           |             |         |  |  |  |

| Number used as a route-thru                    | 2    |           |             |         |  |  |  |

| Number of bonded <u>IOBs</u>                   | 20   | 372       | 5%          |         |  |  |  |

| IOB Flip Flops                                 | 3    |           |             |         |  |  |  |

| Number of BUFGMUXs                             | 1    | 24        | 4%          |         |  |  |  |

| Average Fanout of Non-Clock Nets               | 2.10 |           |             |         |  |  |  |

Fig 9.Design Summary

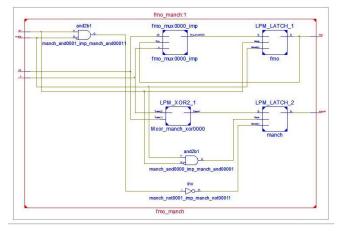

Fig 10.RTL Schematic

### V.CONCLUSION

The coding-decent variety amongst FM0 and Manchester encodings causes the confinement on equipment usage of VLSI engineering plan. A confinement investigation on equipment usage of FM0 and Manchester encodings is talked about in detail. In this paper, the completely reused VLSI engineering utilizing SOLS method for both FM0 and Manchester encodings is proposed. The SOLS method wipes out the confinement on equipment usage by two center strategies: region minimized retiming and adjust rationale activity sharing. The zone conservative retiming moves the equipment asset to decrease 22 transistors. The adjust rationale activity sharing effectively joins FM0 and Manchester encodings with the indistinguishable rationale parts.

### REFERENCES

- [1]. F. Ahmed-Zaid, F. Bai, S. Bai, C. Basnayake, B. Bellur, S. Brovold, et al., "Vehicle safety communications—Applications (VSC-A) final report," U.S. Dept. Trans., Nat. Highway Traffic Safety Admin., Washington, DC, USA, Rep. DOT HS 810 591, Sep. 2011.

- [2]. J. B. Kenney, "Dedicated short-range communications (DSRC) standards in the United States," Proc. IEEE, vol. 99, no. 7, pp. 1162–1182,Jul. 2011.

- ISSN: 2393-9028 (PRINT) | ISSN: 2348-2281 (ONLINE)

- [3]. J. Daniel, V. Taliwal, A. Meier, W. Holfelder, and R. Herrtwich, "Design of 5.9 GHz DSRC-based vehicular safety communication,"IEEE Wireless Commun. Mag., vol. 13, no. 5, pp. 36-43, Oct. 2006.

- [4]. P. Benabes, A. Gauthier, and J. Oksman, "A Manchester code generator running at 1 GHz," in Proc. IEEE, Int. Conf. Electron., Circuits Syst., vol. 3. Dec. 2003, pp. 1156–1159.

- [5]. A. Karagounis, A. Polyzos, B. Kotsos, and N. Assimakis, "A 90nm Manchester code generator with CMOS switches running at 2.4 GHz and 5 GHz," in Proc. 16th Int. Conf. Syst., Signals Image Process., Jun. 2009, pp. 1-4.

- [6]. Y.-C. Hung, M.-M. Kuo, C.-K. Tung, and S.- H. Shieh, "High-speedCMOS chip design for Manchester and Miller encoder," in Proc. Intell. Inf. Hiding Multimedia Signal Process., Sep. 2009, pp. 538-541.

- [7]. M. A. Khan, M. Sharma, and P. R. Brahmanandha, "FSM based Manchester encoder for UHF RFID tag emulator," in Proc. Int. Conf.Comput., Commun. Netw., Dec. 2008, pp. 1-6.

- [8]. M. A. Khan, M. Sharma, and P. R. Brahmanandha, "FSM based FM0 and Mille encoder for UHF RFID tag emulator," in Proc.