# Design and Analysis of Multiplexer and Demultiplexer using different Low Power and High Speed Adiabatic Logic Techniques

B.B.S.Sruthi<sup>1</sup>, Prof.P.V.Sridevi<sup>2</sup> <sup>1</sup>M.Tech student, Andhra University <sup>2</sup>Professor, Andhra University (E-mail: sruthichinnu144@gmail.com)

Abstract - The main objective of this paper is to minimize leakage power dissipation and achieve high performance in digital circuits. Now-a-days, with more devices becoming portable and battery operated, the power dissipation in a device is becoming a major concern. Moreover with the technology change, the number of transistors in a chip is also increasing at a rapid rate. By the increase in more number of transistors in a chip, it occupies more area and subsequently the power dissipation in the form of heat also grows. Adiabatic circuits are the low power circuits where the power dissipation is very less compared to standard CMOS. Adiabatic logic circuits use energy recovery to minimize power dissipation. Following this trend, this paper presents an ADIABATIC LOGIC based design approach for low power and high speed adiabatic 8\*1 Multiplexer and 1\*8 Demultiplexer. Including that some standard adiabatic logic styles like ECRL, 2N2N2P, PFAL are implemented. These adiabatic logic styles have been improved by designing proposed logic. All the simulations are carried out in TANNER EDA TOOL V15.0 at 250nm technology for implementing the design techniques.

**Keywords---**Adiabatic logic, Multiplexer, Demultiplexer, CMOS, ECRL, 2N2N2P, PFAL, Proposed Logic, Delays, Power disisipation, Power saving.

#### I. INTRODUCTION

Due to the shrinking size of systems in today's period of technology, researchers in the field of low power microelectronics have become responsible for handling low power concerns along with reduced size, which in turn increases the power dissipation in the form of heat. The most popular logic for implementing different designs is CMOS logic. Though CMOS technology provides circuits with low static power dissipation during switching operation, but the major concern with CMOS is it has very large switching power consumption, which directly depends on the switching frequency. There are three main sources of power dissipation in digital circuits: dynamic, short circuit, leakage power [1].

$$\begin{split} P_{total} &= P_{static} + P_{dynamic} \\ P_{static} &= P_{sc} + P_{leak} \\ &= I_{sc} \ V_{dd} + I_{leak} \ V_{dd} \\ P_{dynamic} &= C_L V_{dd}^2 f_{clk} \end{split}$$

$P_{static}$  is the static power dissipation of CMOS which includes both short circuit power and leakage power, which is very less compared to other logic circuits.  $P_{dynamic}$  is the dynamic power dissipation which directly depends upon the switching frequency  $f_{clk}$ , combined load capacitance  $C_L$  and is directly proportional to square of supply voltage  $V_{dd}$ . In order to reduce power dissipation in CMOS, the first step to do is to constrict  $V_{dd}$ , but it lowers the performance of the circuit. Another technology parameter is  $C_L$  and it depends on device intrinsic capacitances. In CMOS, the total energy taken from the supply is  $C_L V_{dd}^2$ , in that half of the energy gets dissipated in transistors and the other half is stored in capacitors. The lower bound of energy dissipation in CMOS is (1/2)  $C_L V_{dd}^2$ .

## II. LITERATURE REVIEW

Adiabatic logic is the latest approach for power saving in digital circuits. It is different from static CMOS because instead of using oscillating power supply, it uses the so called power clock. It is also called as "Reversible Logic" because the energy taken from the supply for logic implementation is again given back to the supply. The adiabatic term is taken from thermodynamics, which means "no exchange of heat/energy". Though CMOS technology provides low static power dissipation, during switching operation, currents are generated due to the discharge of load capacitances; it causes the power dissipation that increases with an increase in clock frequency. Such losses were prevented by the adiabatic logic technique, because the charge doesn't flow from the supply voltage to the load capacitance and then to ground, but it flows back to a trapezoidal or sinusoidal supply voltage, the power clock, and the power can be reused [2]. This is the main reason that adiabatic circuits are used as low power VLSI circuits.

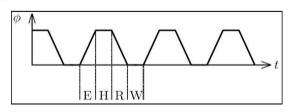

Figure 1.Trapezoidal four-phase power clock

Each of the power clock cycle consists of four intervals as shown in Figure.1, where at the first stage, in the Evaluate (E) interval; the outputs are evaluated from the stable input signals. During the next stage of Hold (H) interval, the outputs are kept stable and then passed to the next subsequent stable input signal. In the Recover (R) stage, the energy is recovered again back from the supply. In the final stage of Wait (W) interval, as for symmetry reasons it is introduced, so similarly for the symmetrical signals also, it becomes easier and more efficient to be executed.

### III. ADIABATIC LOGIC TECHNIQUES

Adiabatic logic circuits are classified into two types as: (a)Partial/Quasi adiabatic logic circuits (b)Full adiabatic logic circuits

(a) Partial/Quasi adiabatic logic circuits: In these circuits, the adiabatic loss occurs when current flows through non-ideal switch, which is proportional to the frequency of the power clock [3]. These circuits have simple architecture and power clock system. Some of the popular partial adiabatic logic circuits are ECRL, 2N2N2P, PFAL, NERL, CAL etc.

(b) Full adiabatic logic circuits: These circuits have no adiabatic loss, because the complete charge on the load capacitance is recovered back by the power supply. The transistor requirement for these circuits is more, so the architecture design is more complex. Some of the full adiabatic logic circuits are PAL, SCRL.

In this paper, the standard partial adiabatic logic techniques like ECRL [2] [4] [7], 2N2N2P [2] [5] [7], PFAL [2] [6] [7] are discussed as follows:

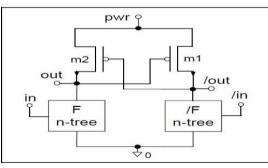

## A. Efficient Charge Recovery Logic (ECRL):

ECRL is suggested by Y.MOON and D.K.JEONG [4]. It is shown in Figure.2; this logic uses two cross-coupled P-MOS transistors M1 and M2 to store the output logic value and also uses two N-MOS transistors blocks for the logic implementation of the ECRL adiabatic logic [8]. The structure of this logic looks like Cascode Voltage Switch Logic (CVSL) with differential signalling. This logic produces full output swing because of the cross-coupled P-MOS transistors in both precharge and recovery phases and as well as this circuit suffers from non-adiabatic loss because of the threshold voltage V<sub>tp</sub> *i.e.*, required to turn ON the PMOS transistors. The amount of loss in ECRL logic is given as:

$E_{ECRL} = C_L |V_{tp}^2|/2$

Figure 2.ECRL General Schematic

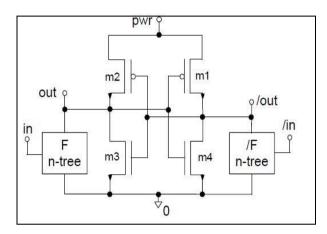

#### *B.* 2N2N2P:

This is one of the logic belongs to quasi adiabatic logic family, which is derived from ECRL in order to reduce coupling effect. This logic consists of two back to back CMOS inverters which are considered as a latch as shown in Figure.3, but the major advantage [9] over ECRL is that it consists of two cross-coupling NMOS switches which leads to non-floating outputs for the major part of the recovery phase. The main difference between ECRL over 2N2N2P is, it has a pair of cross-coupled NMOS transistors instead of cross-coupled PMOS transistors [6]. This logic family is very much similar to standard SRAM cell as it has cross coupled inverters.

Figure 3.2N2N2P General Schematic

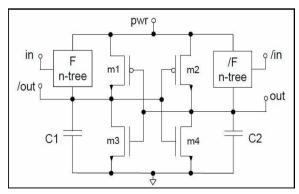

## C. Positive Feedback Adiabatic Logic (PFAL):

This logic is also named as dual rail circuit, because, this logic provides with partial energy recovery [10], [11]. As compared to other similar logic families, PFAL has the lowest energy consumption and a good robustness against technological parameter variations [12]. This circuit is similar to 2N2N2P, but the basic difference to PFAL [5] over 2N2N2P is, two NMOS trees are connected in parallel with two PMOS. The logic implementation of PFAL is done under the two NMOS blocks. The PFAL gates is an adiabatic amplifier, a latch made by two PMOS M1-M2 and two NMOS M3-M4 as shown in Figure.4, because of this it avoids a logic level degradation on the output nodes out and out.

Figure 4.PFAL General Schematic

While the previous paper works are done on Multiplexer based Adiabatic Logic, which involves the usage of NMOS pull down configuration [13], cross coupled inverters [14], Two Phase Drive Adiabatic Dynamic CMOS Logic (2PADCL) [15], now this paper analyses the total power dissipation of the multiplexer and the demultiplexer using different standard logic styles and proposed a new logic style with lesser power dissipation [16], [17], [18].

The paper is précised as follows: the block diagram, truth table and the output expressions of multiplexer and demultiplexer is given in section IV. In section V, proposed logic circuit is described and in section VI, all the schematic designs and their simulated output waveforms are prescribed at 250nm technology. Finally, the comparative analysis based on area per chip based on transistor count, power dissipation and delay is done on section VII.

# IV. EXPRESSIONS FOR MULTIPLEXER AND DEMULTIPLEXER

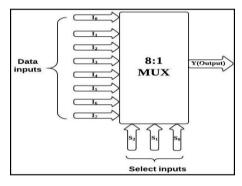

Multiplexer is a combinational logic circuit designed to switch one of several input lines through to a single common output line by the application of a control signal. Multiplexer is also called as "Data Selector". It consists of 'I' given data inputs and 'S' selection inputs which is directly routed to a single output line 'Y' based on selection of inputs [19].

The block diagram of 8\*1 Multiplexer is shown in Figure.5.

Figure 5.Block Diagram of 8\*1 Multiplexer

| Selectio | n Inputs | Out   | put            |

|----------|----------|-------|----------------|

| $S_2$    | $S_1$    | $S_0$ | Y              |

| 0        | 0        | 0     | I <sub>0</sub> |

| 0        | 0        | 1     | $I_1$          |

| 0        | 1        | 0     | $I_2$          |

| 0        | 1        | 1     | I <sub>3</sub> |

| 1        | 0        | 0     | $I_4$          |

| 1        | 0        | 1     | I5             |

| 1        | 1        | 0     | I <sub>6</sub> |

| 1        | 1        | 1     | I <sub>7</sub> |

From the table I, 8\*1 Multiplexer output is deduced in the following way:

$$\begin{array}{l} Y = \overline{S}_{2}\overline{S}_{1}\overline{S}_{0}I_{0} + \overline{S}_{2}\overline{S}_{1}S_{0}I_{1} + \overline{S}_{2}S_{1}\overline{S}_{0}I_{2} + \overline{S}_{2}S_{1}S_{0}I_{3} + \\ S_{2}\overline{S}_{1}\overline{S}_{0}I_{4} + S_{2}\overline{S}_{1}S_{0}I_{5} + S_{2}S_{1}\overline{S}_{0}I_{6} + S_{2}S_{1}S_{0}I_{7} \end{array}$$

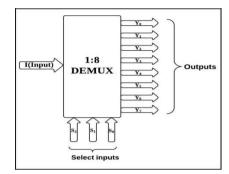

The reverse operation of the digital Demultiplexer is the digital Multiplexer. Demultiplexer is a device that takes a single input line and routes it to one of several digital output lines [16]. It consists of  $2^n$  outputs with 'n' selection lines, which are used to select which output line to send from the input. Demultiplexer is also called as "Data Distributor".

The block diagram of 1\*8 Demultiplexer is shown in Figure.6.

Figure 6.Block diagram of 1\*8 Demultiplexer

TABLE II. Truth table of 1\*8 Demultiplexer

| Se    | election       | on             | Outputs        |                |                |                       |                |       |                |       |

|-------|----------------|----------------|----------------|----------------|----------------|-----------------------|----------------|-------|----------------|-------|

| I     | Inputs         |                |                |                |                | -                     | -              |       |                |       |

| $S_2$ | $\mathbf{S}_1$ | $\mathbf{S}_0$ | Y <sub>7</sub> | Y <sub>6</sub> | Y <sub>5</sub> | <b>Y</b> <sub>4</sub> | Y <sub>3</sub> | $Y_2$ | $\mathbf{Y}_1$ | $Y_0$ |

| 0     | 0              | 0              | 0              | 0              | 0              | 0                     | 0              | 0     | 0              | Ι     |

| 0     | 0              | 1              | 0              | 0              | 0              | 0                     | 0              | 0     | Ι              | 0     |

| 0     | 1              | 0              | 0              | 0              | 0              | 0                     | 0              | Ι     | 0              | 0     |

| 0     | 1              | 1              | 0              | 0              | 0              | 0                     | Ι              | 0     | 0              | 0     |

| 1     | 0              | 0              | 0              | 0              | 0              | Ι                     | 0              | 0     | 0              | 0     |

| 1     | 0              | 1              | 0              | 0              | Ι              | 0                     | 0              | 0     | 0              | 0     |

| 1     | 1              | 0              | 0              | Ι              | 0              | 0                     | 0              | 0     | 0              | 0     |

| 1     | 1              | 1              | Ι              | 0              | 0              | 0                     | 0              | 0     | 0              | 0     |

From the table II, 1\*8 Demultiplexer output is deduced in the following way:

| $Y_0 =$   | $\overline{S}_2 \overline{S}_1 \overline{S}_0 I$ |

|-----------|--------------------------------------------------|

| $Y_1 =$   | $\overline{S}_2\overline{S}_1S_0I$               |

| $Y_2 =$   | $\overline{S}_2 S_1 \overline{S}_0 I$            |

| $Y_{3} =$ | $\overline{S}_2 S_1 S_0 I$                       |

| $Y_4 =$   | $S_2\overline{S}_1\overline{S}_0I$               |

| $Y_{5} =$ | $S_2 \overline{S}_1 S_0 I$                       |

| $Y_{6} =$ | $S_2S_1\overline{S}_0I$                          |

| $Y_{7} =$ | $S_2S_1S_0I$                                     |

|           |                                                  |

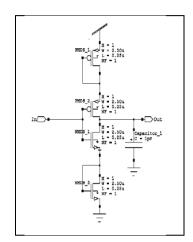

## V. PROPOSED LOGIC CIRCUIT

The proposed logic circuit follows the conventional CMOS logic inverter, which is also driven by a single power supply,  $P_{CLK}$ . The major difference of proposed circuit over CMOS inverter is, it has addition of two extra MOS transistors, one above the PMOS transistor and one below the NMOS transistor as shown in Figure.7, here the pull up end has the extra PMOS transistor and the pull down end has the extra transistor, where these two extra transistors are biased in saturation region as their drain and gate are shorted [16]. Addition of these two transistors results in power reduction of the circuit.

Figure 7.Basic Proposed Logic Inverter Schematic

In the evaluation and precharge phase of the power supply  $P_{CLK}$ , it swings up and down and the voltage that is stored inside the load capacitor  $C_L$  is transferred back to the supply. In this way, the energy is gained back from the output.

# VI. SIMULATIONS AND WAVEFORMS

# A. Standard CMOS (8\*1 Multiplexer):

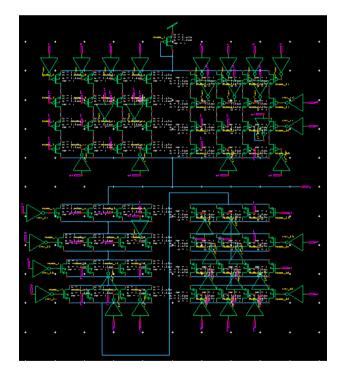

The schematic design of Standard Complementary MOS circuit for 8\*1 Multiplexer is given in Figure.8.

Figure 8.CMOS 8\*1 Multiplexer Schematic Design

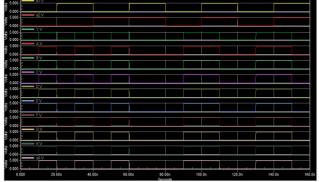

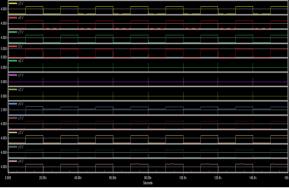

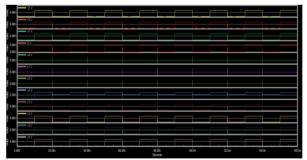

Upon simulation, the output waveform obtained for the CMOS circuit is given in Figure.9.

| - 5000    | s1:V  |        |      |    |     |                |             |     |      |     |     |     |     |       |

|-----------|-------|--------|------|----|-----|----------------|-------------|-----|------|-----|-----|-----|-----|-------|

| 5.000     |       |        |      |    |     |                |             |     |      |     | i   |     |     |       |

| _         |       |        | _    |    |     |                |             |     |      |     |     |     |     |       |

| 16 E      |       |        |      |    |     |                |             |     |      |     |     |     |     |       |

| 0.000-    | Y:V   |        |      |    |     |                |             |     |      |     |     |     |     |       |

| 5.000     |       |        |      |    |     |                |             |     |      |     |     |     |     |       |

| 0.000     | A:V   |        |      |    |     |                |             | _   |      |     |     |     |     |       |

| 5.000     |       |        |      |    |     |                |             |     |      |     |     |     |     |       |

| 0.000-    | B:V   |        |      |    |     |                |             |     |      |     |     |     |     |       |

| 5.000     |       |        |      |    |     |                |             |     |      |     |     |     |     |       |

| < 0.000 + | C:V   |        |      |    |     |                |             |     |      |     |     |     |     |       |

| 5.000     |       |        |      |    |     |                |             |     |      |     |     |     |     |       |

| 0.000     | D:V   |        |      |    |     |                |             |     |      |     |     |     |     |       |

| 5.000     | U.V   |        |      |    |     |                |             |     |      |     |     |     |     |       |

| 0.000+    | EV.   |        |      |    |     |                |             |     |      |     |     |     |     |       |

| 5.000     | - EV  |        |      |    |     |                |             |     |      |     |     |     |     |       |

| 0.000     |       |        |      |    |     |                |             |     |      |     |     |     |     |       |

| 5.000     | - F.V |        |      |    |     |                |             |     | _    |     | _   |     |     |       |

| 0.000     |       |        |      |    |     |                |             |     |      |     |     |     |     |       |

|           | G:V   | _      |      |    |     |                |             |     | _    |     |     | _   |     |       |

| 0.000     |       |        |      |    |     |                |             |     |      |     |     |     |     |       |

|           | - H:V |        |      |    |     |                |             |     |      |     |     |     |     |       |

| 0.000     |       |        |      |    |     |                |             |     |      |     |     |     |     |       |

| 5.000     | s0.V  |        |      |    |     |                |             | _   |      |     |     | _   | _   |       |

| 0.000     |       |        |      |    |     |                |             |     |      |     |     |     |     |       |

| 0.000     | 2     | 20.00n | 40.0 | 0n | 60. | 00n 80.<br>Seo | 00n<br>opda | 100 | 1.0n | 120 | .0n | 140 | l0n | 160.0 |

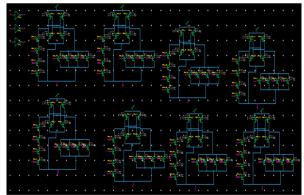

# B. ECRL (8\*1 Multiplexer):

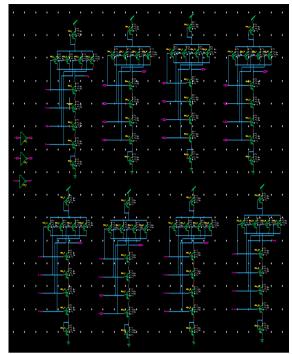

Figure 10.ECRL 8\*1 Multiplexer Schematic Design

The NMOS Pull-down is used for implementing the necessary N-tree logic block (F) and similarly the inversion of  $(\overline{F})$  logic block is designed by using PMOS. The required inputs and its complements for F and  $\overline{F}$  is given according to the selection inputs as shown in Figure.2 &10.

Upon simulation for the above ECRL 8\*1 Multiplexer, the output waveform is given in Figure.11.

| o E s              |        |          |        |          |        |          |        |

|--------------------|--------|----------|--------|----------|--------|----------|--------|

| 0                  | 2:V    |          |        |          |        |          |        |

| V 1.               |        |          |        |          |        |          |        |

|                    | M.     |          |        | /        |        |          |        |

| 0                  |        |          |        | N        |        |          |        |

| , <b>E</b>         | M      |          |        |          |        |          |        |

| 9 E                |        |          |        |          |        |          |        |

| ° 🔚 🖬              | 1/     |          |        |          |        |          |        |

| 0 E                | .v     | N        | - 17   | N        | /      | N        |        |

| 2 <b>–</b> c       | 1      | <u> </u> | V      | <u> </u> | V      | <u> </u> |        |

| 0 E                |        | Ν        |        | N        |        | N        |        |

| :=                 | V      | N        | V      | 1        | V      | A        |        |

| 0 E                | .v.    | N        | 1/     | N        | /      | N        |        |

| <u>الم</u>         |        | <u> </u> | /      | X        | /      |          |        |

| 0.                 | v      | N        | /      | N        | /      | N        |        |

| 0 E                | 1      | <u> </u> | /      |          | /      |          |        |

| V 1                | .v     |          |        |          |        |          |        |

| ° <b>–</b> °       | 1      |          |        |          |        |          |        |

| V 1-               | /      | N        |        |          |        |          |        |

| ° <del>Г – т</del> |        |          |        |          | /      |          |        |

| V 1.               |        |          |        |          |        |          |        |

| s 🗐 s              | 0.17   |          |        |          |        |          |        |

| V 1.               | 0.V    | N        |        | N        |        | N        |        |

| 0                  |        |          |        |          |        |          |        |

| 0.000              | 10.00n | 20.00n   | 30.00n | 40.00n   | 50.00m | 60.00n   | 70.00n |

Figure 11.ECRL 8\*1 Multiplexer Output Waveform

Depending on the selection bits, a particular input is selected from one of the 8 inputs and the outputs for ECRL 8\*1 Mux is based according to the required selection inputs. The outputs are complementary.

## C. 2N2N2P (8\*1 Multiplexer):

Figure 12.2N2N2P 8\*1 Multiplexer Schematic Design

In the 2N2N2P Schematic as shown in Figure.12; here the NMOS logic block is used instead of n-tree and is placed parallel to the Pull-down NMOS transistors as shown in Figure.3. The outputs are complementary.

Upon simulation, the output waveform for the 2N2N2P Schematic is given in Figure.13.

|               |        |          |        |          | <u> </u> |          |        |

|---------------|--------|----------|--------|----------|----------|----------|--------|

|               | v      |          |        |          |          |          |        |

| 00            |        | <u>/</u> |        | <u></u>  |          |          |        |

| 0 S2          | v      |          |        |          |          |          |        |

| 0 <b>-</b> Y3 |        |          |        |          |          |          |        |

| 00            |        |          |        | N        |          |          |        |

| A\            | -      |          |        |          | /        |          |        |

| 00            |        |          |        |          |          |          |        |

| 00-E          |        | \        |        | <u> </u> |          | <u> </u> |        |

| 10 E          | 17     | N        |        | N        | 17       | N        |        |

| 00-E C.V      |        | <u> </u> | 1      | <u> </u> | /        | <u> </u> |        |

| W1.           |        | N        |        |          |          | N        |        |

| 0. E D.V      |        |          | (r     |          | V        |          |        |

| 10 E          | /      | N        | /      | N        | /        | N        |        |

| 00-E          |        |          |        |          |          |          |        |

| W1.           | 1      | \<br>\   |        |          | /        |          |        |

| 00 E          |        |          |        |          |          |          |        |

| 00            | /      |          |        |          |          | <b>`</b> |        |

| 00 G.V        | 1      |          |        |          |          |          |        |

| 00 <b>-</b>   |        |          |        |          |          |          |        |

| 00 — Н.У      |        |          |        |          |          |          |        |

|               |        | Ν        |        | Δ.       | /        |          |        |

| 00 S0:        | V      |          |        |          |          |          |        |

|               | /      | N        | /      |          | /        |          | /      |

| 0.000         | 10.00n | 20.00n   | 30.00n | 40,00n   | 50.00n   | 60.00n   | 70.00n |

|               |        |          |        | Seconds  |          |          |        |

Figure 13.2N2N2P 8\*1 Multiplexer Output Waveform

Depending on the selection input bit combination of 2N2N2P 8\*1 MUX, the output is evaluated.

## D. PFAL (8\*1 Multiplexer):

Figure 14.PFAL 8\*1 Multiplexer Schematic Design

| 0.000    | 10.00n | 20.00n | 30.00n | 40.00n<br>Seconds | 50.00n  | 60.00n | 70.00n |

|----------|--------|--------|--------|-------------------|---------|--------|--------|

| 0.000    | /      |        |        |                   | /       |        |        |

| 5.000    | S0:V   |        |        |                   |         |        |        |

| 5.000 -  | n.v    |        |        |                   |         |        |        |

| 0.000    | H.V    | N      | /      | N                 |         |        |        |

| 5.000    | G.V    |        |        |                   |         |        |        |

| 0.000    |        |        |        |                   |         | N      |        |

| 0.000    | EV     |        |        |                   | · · · · |        |        |

| 5.000 1. | EV     | N      | /      |                   | /       | N      |        |

| 0.000    |        |        | /      |                   |         | 1      |        |

| 5.000    | D:V    |        |        |                   |         |        |        |

| 5.000    |        | Ν      | /      | Λ                 | V       | N      |        |

| 0.000    | C:V    |        |        |                   |         |        |        |

| 0.000 1  | B:V    | N      | /      |                   | /       | N      |        |

| 0.000    | 21/    |        | /      | <u> </u>          |         | \      |        |

| 5.000    | A.V    |        |        |                   |         |        |        |

| 5.000    |        |        |        |                   |         |        |        |

| 0.000    | Y:V    |        |        | /                 |         |        |        |

| 5.000 1. | S2:V   |        |        |                   |         |        |        |

| 0 000-E  |        |        |        |                   |         | /      |        |

| 5.000    | S1:V   |        |        |                   |         |        |        |

Figure 15.PFAL 8\*1 Multiplexer Output Waveform

Upon simulation, the output waveform for PFAL is obtained according to selection bit inputs.

## E. PROPOSED LOGIC CIRCUIT (8\*1 Multiplexer):

The proposed logic is very much similar to CMOS circuit except the proposed logic uses two extra transistors, one PMOS above the pull-up and one NMOS below the pull-down where both the gate and drain are shorted in both pull-up and pull-down devices as shown in Figure.7. Hence, both the devices operate in saturation region. The outputs are not complementary [16]. The Schematic of proposed logic circuit is given in Figure.16.

Figure 16.Proposed Logic 8\*1 Multiplexer Schematic Design

Based on the simulation, the output waveform for the Proposed Logic Schematic circuit design is shown in Figure.17.

Figure 17. Proposed Logic 8\*1 Multiplexer Output Waveform

The outputs for the Proposed Logic are obtained regarding the selection bit inputs.

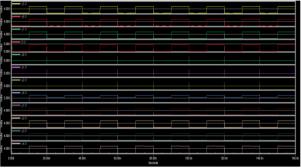

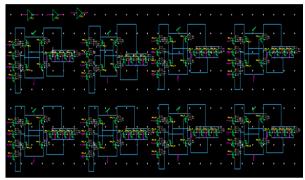

# F. Standard CMOS (1\*8 Demultiplexer):

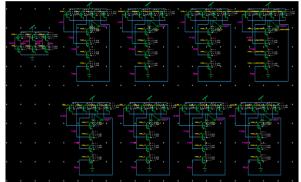

The schematic design of Standard Complementary MOS circuit for 1\*8 Demultiplexer is given in Figure.18.

Figure 18.CMOS 1\*8 Demultiplexer Schematic Design

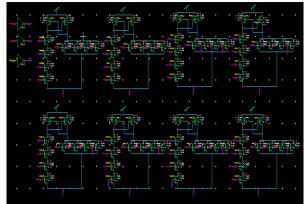

Upon simulation, the output waveform obtained for the CMOS Demux circuit is given in Figure.19.

| 0<br>y6.V        |        |        |        |        |        |        |        |  |

|------------------|--------|--------|--------|--------|--------|--------|--------|--|

| 0 yev            |        |        |        |        |        |        |        |  |

| y7.V             |        |        |        |        |        |        |        |  |

| 0<br>D.V         |        |        |        |        |        |        |        |  |

|                  |        |        |        |        |        |        |        |  |

| o stv            |        |        |        |        |        |        |        |  |

| 0 s1.V           |        |        |        |        |        |        |        |  |

| 0<br>            |        |        |        |        |        |        |        |  |

| 1                |        |        |        |        |        |        |        |  |

| 0<br>0 y1.V      |        |        |        |        |        |        |        |  |

| y1.V             |        |        |        |        |        |        |        |  |

|                  |        |        |        |        |        |        |        |  |

| 0 <u>y</u> 2.V   |        |        |        |        |        |        |        |  |

| ν <sub>2</sub> γ |        |        |        |        |        |        |        |  |

| •                |        |        |        |        |        |        |        |  |

| 0 y4.V           |        |        |        |        |        |        |        |  |

| 0 <b>E</b>       | 20.001 | 40.00n | 60.001 | 80.001 | 100.01 | 120.01 | 140.0n |  |

Figure 19.CMOS 1\*8 Demultiplexer Output Waveform

# G. ECRL (1\*8 DeMultiplexer):

The schematic design of ECRL circuit for 1\*8 Demultiplexer is given in Figure.20.

Figure 20.ECRL 1\*8 Demultiplexer Schematic Design

Upon simulation, the output waveform obtained for ECRL Demux circuit is given in Figure.21.

Figure 21.ECRL 1\*8 Demultiplexer Output Waveform

After the simulation, the outputs for ECRL are obtained according to the selection bit inputs.

# H. 2N2N2P (1\*8 DeMultiplexer):

Figure 22.2N2N2P 1\*8 Demultiplexer Schematic Design

In the 2N2N2P Schematic as shown in Figure.22, here the NMOS logic block is used instead of both n-tree (F and  $\overline{F}$ ) and is placed parallel to the Pull-down NMOS transistors as shown in Figure.3. The outputs are complementary.

Upon simulation, the output waveform obtained for 2N2N2P Demux circuit is given in Figure.23.

Figure 23.2N2N2P 1\*8 Demultiplexer Output Waveform

I. PFAL (1\*8 DeMultiplexer):

Figure 24.PFAL 1\*8 Demultiplexer Schematic Design

In the PFAL schematic as shown in Figure.24; the two cross-coupled CMOS inverters are connected back to back and the NMOS logic block is used instead of n-tree for both (F and  $\overline{F}$ ) and is kept parallel to the PMOS logic blocks. The outputs are complementary.

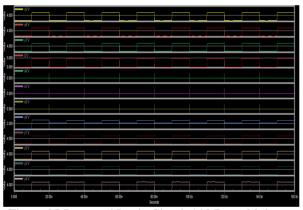

Upon simulation, the output waveform obtained for PFAL Demux circuit is given in Figure.25.

Figure 25.PFAL 1\*8 Demultiplexer Output Waveform

# J. PROPOSED LOGIC CIRCUIT (1\*8 DeMultiplexer):

The schematic design of Proposed Logic circuit for 1\*8 Demultiplexer is given in Figure.26.

Figure 26.Proposed Logic Circuit 1\*8 Demultiplexer Schematic Design

Upon simulation, the output waveform obtained for PFAL Demux circuit is given in Figure.27.

Figure 27.Proposed Logic Circuit 1\*8 Demultiplexer Output Waveform

## VII. POWER CONSUMPTION ANALYSIS AND COMPARISON

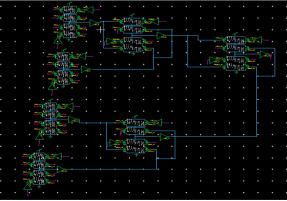

All the schematic designs of proposed logic design and standard adiabatic logic styles like ECRL, 2N2N2P, PFAL and CMOS logic style for both the Multiplexer and Demultiplexer are done using TANNER EDA TOOL V15.0 and the simulations are done using T-SPICE. Their power consumption outputs are carried out at 250nm technology with W = 2.5u and L = 250n, and the DC supply voltage,  $V_{DD} = 5v$ .

# A. 8\*1 Multiplexer:

Table III & IV shows the performance of the Multiplexer for the Proposed Logic over the Standard adiabatic logic styles in terms of Transistor count, Area per chip, Delay and most significantly the Power Dissipations as well as it presents the percentage of Power Saving of the Proposed Logic with respect to the standard adiabatic logic styles.

| TABLE III. PERFORMANCE ANALYSIS OF VARIOUS LOGIC |

|--------------------------------------------------|

| STYLES FOR 8*1 MULTIPLEXER AT 250nm TECHNOLOGY   |

| Parameter                             |       |       | vles   | es    |          |  |

|---------------------------------------|-------|-------|--------|-------|----------|--|

|                                       | CMOS  | ECRL  | 2N2N2P | PFAL  | PROPOSED |  |

| Transistor<br>Count                   | 77    | 64    | 56     | 46    | 75       |  |

| Area Per<br>Chip(µm <sup>2</sup> )    | 19.25 | 16    | 14     | 11.5  | 18.75    |  |

| Delay (ns)                            | 79.11 | 52.72 | 64.54  | 69.42 | 49       |  |

| Total<br>Power<br>Dissipation<br>(µW) | 0.412 | 0.140 | 0.171  | 0.121 | 0.012    |  |

TABLE IV. PERCENTAGE POWER SAVING OF PROPOSED LOGIC WITH RESPECT TO STANDARD LOGIC STYLES FOR 8\*1 MULTIPLEXER

| LOGIC<br>STYLES         | CMOS   | ECRL   | 2N2N2P | PFAL  |

|-------------------------|--------|--------|--------|-------|

| % OF<br>POWER<br>SAVING | 97.04% | 91.34% | 92.8%  | 89.9% |

From the Tables III & IV, it can be inferred that the proposed logic for the multiplexer shows the least power dissipation and delay when compared to adiabatic logic styles and standard CMOS style. The percentage power savings of 89.9% over PFAL, 91.34% over ECRL, 92.8% over 2N2N2P and 97.04% over CMOS shows significant improvement over the standard logic styles. For a system comprising of many such multiplexers, the power saving will be large and the efficiency of the circuit will be high because of the reduction in delay.

## B. 1\*8 Demultiplexer:

Similarly, for the Demultiplexer, the Tables V & VI shows the performance analysis and percentage power savings of the Proposed Logic with respect to the standard adiabatic logic styles.

# TABLE V. PERFORMANCE ANALYSIS OF VARIOUS LOGIC STYLES FOR 1\*8 DEMULTIPLEXER AT 250nm TECHNOLOGY

| Parameter                             | Logic Styles |       |        |        |          |  |

|---------------------------------------|--------------|-------|--------|--------|----------|--|

|                                       | CMOS         | ECRL  | 2N2N2P | PFAL   | PROPOSED |  |

| Transistor<br>Count                   | 78           | 83    | 99     | 99     | 83       |  |

| Area Per<br>Chip(µm <sup>2</sup> )    | 19.5         | 20.75 | 24.75  | 24.75  | 20.75    |  |

| Delay (ns)                            | 65.37        | 40.29 | 58.96  | 55.25  | 35.45    |  |

| Total<br>Power<br>Dissipation<br>(µW) | 0.346        | 0.370 | 0.3895 | 0.3397 | 0.077    |  |

TABLE VI. PERCENTAGE POWER SAVING OF PROPOSED LOGIC WITH RESPECT TO STANDARD LOGIC STYLES FOR 1\*8 DEMULTIPLEXER

| LOGIC<br>STYLES         | CMOS   | ECRL   | 2N2N2P | PFAL   |

|-------------------------|--------|--------|--------|--------|

| % OF<br>POWER<br>SAVING | 77.74% | 79.18% | 80.2%  | 77.33% |

From the Tables V & VI, it can be clearly observed that the proposed logic for the Demultiplexer shows the least power dissipation and delay when compared to adiabatic logic styles and standard CMOS style. The percentage power savings of 77.33% over PFAL, 77.74% over CMOS, 79.18% over ECRL and 80.2% over 2N2N2P indicates its superiority over the standard logic styles. For a system comprising of many such demultiplexers, the power saving will be enormous and gives high efficiency over speed.

## VIII. CONCLUSION

Adiabatic logic is an efficient technique for designing low power circuits compared to standard CMOS logic. Simulation indicates it is a power saving logic. From the analysis we can conclude that the logics for the Multiplexer and the Demultiplexer over the proposed logic show the least power dissipation and highest efficiency in speed with reduction in delay parameter when compared to adiabatic logic styles and standard CMOS style. The future scope of this work is that multiplexers and demultiplexers with highest number of input and output lines can be constructed by cascading the proposed ones.

## ACKNOWLEDGEMENT

#### I would like to express my gratitude to Prof.

**P.V.SRIDEVI**<sub>M.E.,Ph.D.</sub>, Professor, Department of Electronics and Communication Engineering, for her invaluable guidance, advice and supporting me in successfully doing this project.

## REFERENCES

- S.Vijaykumar and B.Karthikeyan, "Mixed Style of Low Power Multiplexer Design for Arithmetic Architectures using 90nm Technology", Proceedingsof the 12<sup>th</sup> international conference on Networking, VLSI and signal processing (ICNVS), pp.83-87, February 2010.

- [2] P.Teichmann, "Adiabatic Logic Future Trends and Future Level Perspective", Springer publication, 2012 Edition.

- [3] Deepti Shinghal, Amit Saxena, Arti Noor, "Adiabatic Logic Circuits: A Retrospect", MIT International Journal of Electronics and Communication Engineering, Vol.3, No.2, pp. 108-114, August 2013.

- [4] Yong Moon and Deog-Kyoon Jeng, "An Efficient Charge Recovery Logic Circuit", IEEE Journal of Solid State Circuits, Vol.31 Issue 4, pp. 514-522, April 1996.

- [5] A. Vetuli, S. Di Pascoli, L.M. Reyneri, "Positive Feedback In Adiabatic Logic", Electronics Letters, Vol. 32 Issue 20, pp. 1867-1869, September 1996

- [6] A. Kramer, J.S. Denker, B.Flower, J. Moroney, "2<sup>nd</sup> order adiabatic computation with 2N-2P and 2N2N2P logic circuits", Proceedings of the International Symposium on Low power design (ISLPED), pp. 191-196, April 1995.

- [7] Ettore Amirante, Agnese Bargagli-Sto, Jurgen Fischer, Giuseppe Iannaccone, and Doris Schmitt-Landsiedel, "Variations of the Power Dissipation in Adiabatic Logic Gates", International Workshop on Power And Timing Modelling, Optimization and Simulation (PATMOS), pp. 9.1.1-9.1.10, September 2001.

- [8] Sung-Mo Kang and Yusuf Leblebici, CMOS Digital Integrated Circuits-Analysis and Design, McGraw-Hill, 2003.

- [9] J. Rabey, M. Pendram, ""Low Power Design Methodologies", Kluwer Academic Publishers, 5<sup>th</sup> edition, pp 5-7, 2002.

- [10] Mukesh Tiwari, Jai Karan Singh, Yashasvi Vaidhya, "Adiabatic Positive Feedback Charge Recovery Logic For Low Power CMOS Design", IJCTEE, Volume 2, Issue 5, October 2012.

- [11] B. Dilli Kumar, M. Bharathi, "Design of Energy Efficient Arithmetic Circuits Using Charge Recovery Adiabatic Logic", International Journal of Engineering Trends and Technology, Volume 4, Issue 1, 2013.

- [12] T.Gabara, "Pulsed Power Supply CMOS", Technical Digest IEEE Symposium Low Power Electronics, San Dieogo, pp. 98-99, October 1994.

- [13] F. Liu and K. T. Lau, "Pass-transistor adiabatic logic with NMOS pull-down configuration", Electronics Letters, Vol.34, Issue 8, pp. 739-741, April 1998.

- [14] Richa Singh and Rajesh Mehra, "Power Efficient Design of Multiplexer Using Adiabatic Logic", International Journal of advances in Engineering & Technology (IJAET), Vol. 6, Issue 1, pp. 246-254, March 2013.

- [15] Varun Singh, Maan Singh, Tarun Arora, Ankit Kaushik and Praveer Saxena, "Design Of 2:1 Multiplexer Using Two Phase Drive Adiabatic Dynamic CMOS Logic For Low Power Applications", International Journal of Engineering Research and Applications (IJERA), Vol. 3, Issue 1, pp. 1582-1590, January-February 2013.

- [16] Shruti Konwar, Thockchom Brijit Singha, Soumik Roy, Reginald H.Vanlalchaka, "Adiabatic Logic Based Low Power Multiplexer And Demultiplexer", International Conference On Computer Communication and Informatics (ICCCI-2014), Jan 03-05, 2014.

- [17] Arun Kumar, Manoj Sharma, "Design and Analysis of Multiplexer using Adiabatic techniques ECRL and PFAL", International Conference On Advances In Computing, Communications And Informatics (ICACCI), 2013.

- [18] V. C. Athas, L. Svensson, J. G. Koller etc., N. Tzartzanis and E. Y. Chou: "Low Power Digital Systems Based on Adiabatic Switching Principles", IEEE Transactions on VLSI Systems, Vol. 2, No. 4, pp. 398-407, December 1994.

- [19] S. Prashanth, Prashant K.Shah, "Design and Analysis of Mutliplexer in Different Low Power Adiabatic Techniques", International Journal Of Innovative Research In Computer And Communication Engineering (IJIRCCE), MAY 2016.

B.B.S.SRUTHI received her B.Tech in Communication Electronics and Gayatri Vidva from Engineering Parishad College of Engineering for Women, Visakhapatnam in 2015 with 78% of CGPA and M.Tech in VLSI University, from Andhra Visakhapatnam with 82% of CGPA in 2018. Her area of interest is VLSI design.

Prof.P.V.SRIDEVI received her B.Tech in Electronics Communication Engineering from Nagarjuna University in 1986. In M.E, she obtained a Masters degree in Applied Electronics from Bharithiar University in 1988 and received PhD degree from Andhra University in 1997. Now, she is working as a Professor in the Department of Electronics and Communication Engineering, Andhra University. She is awarded with Gold Medal by Parvataneni Brahmayya Memorial Trust, 1986 and Sir Thomas Ward Memorial Gold Medal by the Institution of Engineers (INDIA), 1989. Her research interests include Antennas and VLSI design.